Franklin W. Olin College of Engineering

Proceedings of

## CA 2004

the

## Fall 2004 ENGR 3410 Computer Architecture Class

<ca@lists.olin.edu>

Needham, Massachusetts, December 2004

# Contents

| Preface                                                             |    |

|---------------------------------------------------------------------|----|

| Mark L. Chang                                                       | ii |

| Digital Signal Processors                                           |    |

| Grant R. Hutchins, Leighton M. Ige                                  | 2  |

| FPGA Architecture, Algorithms, and Applications                     |    |

| Kathleen King, Sarah Zwicker                                        | 7  |

| A History of Nintendo Architecture                                  |    |

| Jesus Fernandez, Steve Shannon                                      | 13 |

| Graphical Processing Units: An Examination of Use and Function      |    |

| Michael Crayton, Mike Foss, Dan Lindquist, Kevin Tostado $\ .\ .$   | 17 |

| Dual Core On-Chip Multiprocessors and the IBM Power5                |    |

| Thomas C. Cecil                                                     | 24 |

| Pong on a Xilinx Spartan <sup>3</sup> Field Programmable Gate Array |    |

| Kate Cummings, Chris Murphy, Joy Poisel                             | 28 |

| The PowerPC Architecture: A Taxonomy, History, and Analysis         |    |

| Alex Dorsk, Katie Rivard, Nick Zola                                 | 32 |

| A Brief Introduction to Quantum Computation                         |    |

| Michael W. Curtis                                                   | 38 |

| Beauty and the Beast: AltiVec and MMX Vector Processing Units       |    |

| Drew Harry, Janet Tsai                                              | 44 |

| VLIW and Superscalar Processing                                     |    |

| Sean Munson, Clara Cho                                              | 49 |

## Preface

The members of the Fall 2004 ENGR 3410 Computer Architecture class are pleased to present the Proceedings of CA 2004. This is the first offering of the class, and this document represents only a portion of the work done by the students this semester. Presented here are the final papers describing their end of semester projects.

The students were given a few weeks to research any Computer Architecture topic that interested them. The deliverables included a brief in-class presentation as well as the documents compiled here. The goal of the project was to encourage group learning of advanced Computer Architecture topics not covered in class and give the students a chance to develop independent research skills.

The projects were wonderfully varied, ranging from literature reviews to actual hardware implementations. It is important to note for the reader that several students chose to complete an optional lab as part of the final project and implemented a pipelined MIPS processor in Verilog. This work is not reflected in these proceedings, however the scope of these students' research projects were adjusted accordingly.

As the instructor for CA 2004, I am most proud of the work accomplished by the students this semester. I would like to thank them for their hard work and their creative zeal. For more information regarding Computer Architecture at F. W. Olin College of Engineering, please visit our class web page at http://ca.ece.olin.edu.

Mark L. Chang Assistant Professor Franklin W. Olin College of Engineering

## **Digital Signal Processors**

Grant R. Hutchins, Leighton M. Ige

Abstract—Digital Signal Processors (DSPs) operate on digital signals in realtime applications. They have several benefits over other processor architectures, due to specialized designs and instruction sets. This article offers an overview of general properties of DSPs and comments on their applications in the real world.

## I. INTRODUCTION

We live in an analog world composed of continuous functions: the light you see, the sound you hear, and the words you speak. However, for many reasons these signals are converted into digital representations for processing and transmission. It is often cheaper, more accurate, and computationally simpler to manipulate a digital representation of a continuous signal, since there are discrete time slices of data to process instead of a signal with infinite resolution. The power of the digital revolution lies in the ability of digital systems to approximate the analog world. Once in a discrete representation, signals can be digitally processed to have different effects, such as the reduction of background noise in a microphone feed or the encryption and compression of a cell phone call.

Digital signal processors (DSP) are specific microprocessors that specialize in the manipulation of signals in real time. In the specific applications of devices that interface with the world, live inputs must be sampled, processed, decoded, and outputted on the fly. Thus, DSPs must be designed to be able to complete a lot of computations very quickly to be effective. The rate at which these DSPs operate must be at least as fast as the rate of its input, otherwise backlogs will be created. Once the process no longer proceeds in real time you lose the synchronization between inputs and outputs, with the signal becoming decoupled. This scenario can be likened to that of a cell phone conversation in which you had to wait a long time for your phone to decode the received audio signal from your correspondent. When there is too long of a delay many of the benefits of a synchronous conversation are lost and one would be no worse off sending a written letter.

Today, by far, the largest implementation of DSPs is in cell phones. Every cell phone sold contains a DSP, which is necessary to perform all the encoding and decoding of the audio signals which are transmitted through the wireless communications network. Additionally, most new phones now have advanced multimedia capabilities which need to be processed in real time. These functions such as picture taking, music playing, and video recording, along with their nonintegrated device counterparts, require DSPs for many fast computations. DSPs can be found at the core of many of the products in the growing multimedia device segment.

Within the audio domain, DSPs are rather prevalent and can be found in CD players as well as high end home audio

components. Many audio receivers offer the capability of real time equalization adjustments to audio playback. The computationally intensive algorithms for transforming audio to sound as if it is being played in a large concert hall or a dance hall are handled by DSPs. Additionally, many filtering and noise reduction algorithms can be implemented to clean up audio signals. Convolution and Fast Fourier Transforms require many sequential multiplications and additions, a procedure for which DSPs are optimized.

DSPs are also very flexible in their implementation as they can be reprogrammed to perform different calculations. For example, a cell phone provider could decide to support a new data feature on its phones. The DSP could then be updated to decode the new data packets being sent to the phone.

While there are currently many DSPs implemented in everyday devices, they are becoming more prevalent due to their high performance, flexibility, and continually decreasing prices. The capability to perform complex manipulations on data in real time can enable many systems to incorporate more inputs from the world.

## II. COMMON DSP TASKS

In digital signal processing, a few simple types of algorithms dominate. Thus, DSPs highlight their abilities to perform functions to

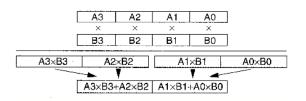

## A. Multiply-Accumulate

Time domain filters are a common operation in digital signal processing. Digital filters are implemented by taking streams of current and prior input and output data, scaling them with coefficients that perform a certain filter function, and summing them to generate the next output.

Some filters have hundreds or thousands of coefficients. Each of these multiplication operations must occur in order to generate each output sample. However, data rates in audio DSP applications are often as high as 96,000 samples per second (video can go much higher), meaning that millions of multiplications and accumulations must happen every second. For this reason, DSPs are optimized for and benchmarked on their ability to perform multiply-accumulate operations. A common metric for DSP processors is MMACS, or millions of multiply-accumulates per second.

## B. Fast Fourier Transform (FFT)

In most situations, signal data is represented in the time domain. That is, each separate word of signal data represents a discrete sample of the signal in time. However, many functions, such as equalization and pitch-shifting, operate on

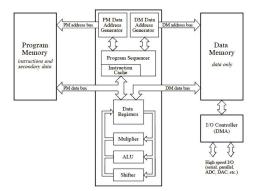

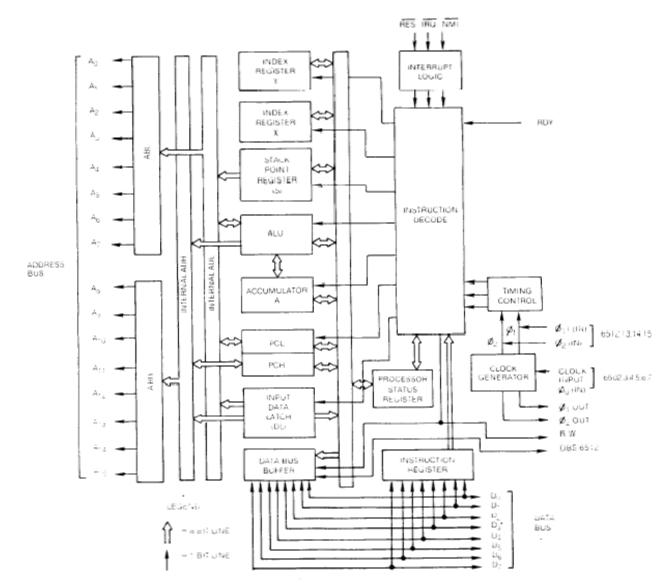

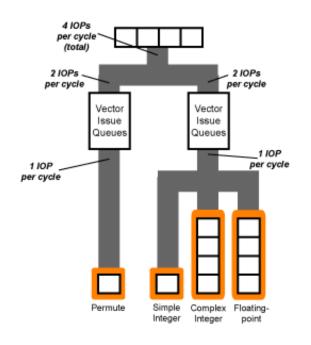

Fig. 1. Typical architecture for a DSP (taken from[1])

the frequency domain, where each word represents the amount of information present in the signal at a particular frequency.

The Fast Fourier Transform is an algorithm which takes time domain data and converts it into corresponding frequency domain data. In order to do so, the data must be reshuffled and processed through multiple loops. Using a similar routine, the Inverse Fast Fourier Transform converts frequency domain data back into time domain data.

## III. ARCHITECTURE AND DATAPATH

DSPs have several architectural properties that set them apart from other classes of processors. Each optimization has the common applications of DSPs in mind and aims to reduce the overhead associated with manipulating large digital signals in a repetitive fashion.

## A. Memory

DSPs access memory in differing ways. Unlike traditional microprocessors, some DSPs have two data buses and memory files, which allows for better performance.

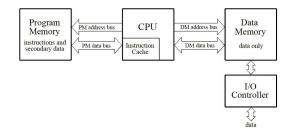

1) Von Neumann Architecture: The von Neumann architecture, named after the important mathematician John von Neumann, contains a single memory bus connected to a single processor. In this simple architecture, one memory file contains both instructions and data.

The data bus in the von Neumann architecture is serial, allowing only one value to be read from memory at a time. Consider a simple multiply-add instruction, which involves multiplying two values and adding them to a third value. This instruction requires three separate fetches from memory, namely the instruction, the two multiplication operands, and the addition operand.

If the memory is clocked at the same speed as the main processor, then this multiply-add example will necessarily take at least four clock cycles to complete. Therefore, some DSP chips use a modified von Neumann architecture in which clock the memory at a multiple of the processor clock and thus allow a single instruction to access multiple memory locations in one clock cycle.

Fig. 2. Super Harvard Architecture (taken from [1])

2) Harvard Architecture: The Harvard architecture was developed by a group led by Howard Aiken at Harvard University during the 1940s. The Harvard architecture employs two separate memories, one for instructions and one for data. The processor has independent buses, so that program instructions and data can be fetched simultaneously.

Most DSPs use some sort of Harvard architecture. However, most digital signal processing routines are data intensive and thus require more than one load from data memory for each load from instruction memory. The original Harvard architecture does not support

*3) Super Harvard Architecture (SHARC:* Some products from Analog Devices use what they call a "Super Harvard architecture" (SHARC), such as their ADSP-2016x and ADSP-211xx families of DSPs. The SHARC processors add an instruction cache to the CPU and a dedicated I/O controller to the data memory.

The SHARC instruction cache takes advantage of the fact that digital signal processing routines make use of long repetitive loops. Since the same instructions are performed over and over, the instruction bus does not need to repeatedly access the instruction memory. Cache hits will happen a vast majority of the time, freeing the instruction bus to allow the CPU to read an additional operand.

However, since the freed bus connects to instruction memory, the programmer must place one set of operand data in instruction memory and the other in regular data memory. This requirement adds complexity to the organization of DSP application programs, but increases the throughput significantly.

The dedicated I/O controller connects directly to the data memory, allowing signals to be written and read to RAM directly at very high speeds without using the CPU. For example, some of Analog Devices's models have two serial ports and six parallel ports which each operate on a 40 MHz clock. Using all six ports together gives data transfer at 240 MHz, which is more than enough for most real-time DSP applications and helps speed asynchronous processing. Some processors also include analog-to-digital and digital-toanalog converters, and thus can input and output analog signals directly.

Fig. 3. Circular buffer, before and after incrementing loop

## B. Addressing

DSPs have some optimizations that allow them to read memory more efficiently for digital signal processing tasks.

1) Circular Buffers: A circular buffer, shown in 3 is a continuous section of memory that a DSP increments through repeatedly, looping back to the first position after it accesses the final position. DSPs often contain Data Address Generators (DAGs) that can control multiple circular buffers. Each DAG holds the memory location, size, and other information about a particular circular buffer. In addition, a DAG can perform logic on these variables such as loop incrementing. This logic prevents applications from needing to tie up the processor with instructions to perform math and branching in order to keep repetitive loops running.

2) *Bit-reversed Addresses:* In addition to managing circular buffers, DAGs can be switched into a special bit-reversed mode in which the order of the address bits is inverted. Part of the Fast Fourier Transform algorithm involves inverting the bit order of the addresses which point to the data and then sorting the resulting addresses. This process shuffles the addresses, allowing the DSP to operate on the pieces of data in precisely the order the FFT algorithm calls for.

## C. Parallelism

DSPs are optimized to run several unrelated options all at once. For instance, a DSP might allow a multiplier, an arithmetic logic unit, and a shifter to run in parallel, each processing a different value from a data register. For example, an Analog Devices SHARP processor can perform a multiply, an addition, two data moves, update two circular buffer pointers, and perform loop control all in one clock cycle.

On traditional microprocessors each of these procedures might take its own instruction. Instead of performing loop logic after each iteration, a program could instead perform a few initialization instructions which tell the DSP how to automatically loop through the next set of instructions, which for a typical loop might reduce the number of clock cycles by a factor of ten or more from that of a traditional microprocessor.

## D. Precision

Not all DSPs represent numerical values in the same way. Depending on the application and certain trade-offs in performance and price, one representation might make more sense than another.

1) Fixed-point: The cheapest and most basic types of DSPs perform operations on fixed-point numbers. At the most basic level, all DSPs must be able to manipulate integers, in order to process loops, access memory locations, and perform other basic operations.

For fixed-point representation, DSPs often employ a "fractional" notation in addition to the standard integer notation. Fractional notation places all values between 0 and 1 for unsigned fractions and -1 and 1 for signed fractions. For example, a 16-bit unsigned fraction representation has 65,536 different possible values, ranging evenly from 0 to 1. A fractional notation is useful for multiply-accumulate operations, since coefficients for finite impulse response and infinite impulse response filters need to be less than 1 in order to prevent excessive resonance.

2) Floating-point: For higher quality applications, DSPs often employ floating-point representations. The most common format, ANSI/IEEE Std. 754-1985, has 32-bit words and ranges from as high as  $\pm 3.4 \times 10^{38}$  and as low as  $\pm 1.2 \times 10^{-38}$ , a range that dwarves that of comparable fixed-point representations.

However, since floating-point values often have twice as many bits per word as fixed-point values, data buses must be doubled in width. If memory is located off-chip, this translates to many more pins, leading to more difficult board layouts. Also, the larger size of words takes up more memory to represent the same amount of data.

Another important feature of floating-point representation is that the difference between two adjacent numbers is proportional to their values. In 16-bit fixed-point fractional notation two adjacent values might be separated by a difference as low as one-tenth the value, as with  $\frac{10}{32,767}$  and  $\frac{11}{32,767}$ , for example. In the standard 32-bit floating-point representation, the difference between two adjacent numbers is set at about ten-millionth times smaller than their value.

The higher resolution of floating-point values allows for a higher signal-to-noise ratio. Since multiple multiplyaccumulate operations introduce rounding errors over time, fixed-point representations have significant noise. Overall, using a standard deviation method to measure noise, 32-bit floating point outperforms 16-bit fixed-point by a factor of about 3,000.

*3) Extended precision:* Consider a routine that involves 100 fixed-point multiply-accumulate instructions. Since each instruction introduces a significant amount of noise, the final result has accumulated 100 times the noise of each instruction.

In order to prevent this situation, most DSP architectures have intermediate fixed-point registers of much higher resolution. For example, a 16-bit floating-point DSP might have a 40-bit extended precision accumulator, only stepping the signal down to 16-bit once the final value is ready to be written to memory.

## **IV. SPECIAL DSP INSTRUCTIONS**

DSP processors have highly specialized instruction sets which allow assemblers and assembly programmers to get the best performance out of their architectures. Consider the following examples found at [2] from the Lucent DSP32C processor instruction set.

## A. Parallel modification of address pointers

One common technique in DSP instructions is to manipulate the value of registers acting as pointers to memory. This manipulation occurs whenever the address of the register appears in code, depending on how it is referenced. For example, think of an assembly programmer implementing a multiply-accumulate operation using a value from memory that is pointed to by the register rP. The programmer can also tell the processor to increment the register in the same instruction by calling the register rP++ right in the assembly code. Unlike in general purpose processors, the increment operator happens immediately within another instruction rather than requiring an instruction unto itself. A similar post-decrement can occur after reading the value. The Lucent DSP32C can perform as many as three of these pointer modifications, while performing another function, all within one instruction.

#### B. Bit-reversed post-increment

A highly specific instruction found in the Lucent DSP32C is the bit-reversed post-increment. Within one instruction, as in the previous example, the processor can also increment the pointer to the next value in an array as if the address were in reverse order. This bit-reversed traversal of an array only ever gets used for FFTs and inverse FFTs in practice. Frequency domain operations are common enough in digital signal processing that chip designers spend the extra hard work to incorporate this highly specialized feature. With this special instruction, DSPs can perform real-time FFT and frequency domain functions, whereas most general purpose processors might only be able to perform frequency domain operations asynchronously.

### C. Instruction length

Due to the number of operations that DSP processors perform in parallel, some specialized designs have emerged. Some processors with 32-bit instructions, for example, have an option to run two 16-bit multiply-accumulate instructions in one clock cycle. In addition, some DSPs have moved toward a Very Long Instruction Word (VLIW), as big as 64 bits in width, to run several operations in parallel. A VLIW instruction gives the programmer limited control over which four 16-bit sub-instructions should run in parallel.

## V. ADVANTAGES OF DSPS OVER OTHER PROCESSORS

Digital Signal Processors perform operations that focus entirely on specific applications, such as MP3 decompression or realtime video filters. However, DSPs are not the only processors able to perform these tasks. Every day millions of people listen to MP3s on their desktop computers, for example. There are several alternatives to DSPs, each with its own benefits and problems.

## A. Field-Programmable Gate Arrays (FGPAs)

Field-Programmable Gate Arrays (FPGA) are logic chips that can, as the name implies, be reprogrammed in the field to have entirely different functionality. An FPGA is programmed with a certain desired gate array and operates accordingly. Thus it is very fast in that its implementation is customized for the particular task at the gate level. It is essentially like achieving custom silicon results without the hurdle of actually manufacturing a unique chip. When the desired operation of the FPGA changes, a new gate array can be written over the chip.

An FPGA would seem to be a viable alternative to a DSP as it could be customized for the same sorts of computationally intensive tasks. While the FPGA would certainly be faster than the DSP due to its dedicated logic, it is much more expensive and requires more energy. Additionally, until recently many FPGAs did not offer enough programmable gates to provide the full functionality of a DSP. In an attempt to address this deficiency, FPGAs are being manufactured with enhanced DSP features to enable this capability. While the DSPs have a significant price advantage at under at average of \$6 per chip [3], the added flexibility of a DSP-capable FPGA could justify the additional expense.

## B. Application-Specific Integrated Circuits (ASICs)

Application-Specific Integrated Circuits (ASIC) are essentially customized silicon chips that are specifically configured for a particular task. ASICs are very efficient in their execution of tasks and utilize very dissipate very little power. However, a big limitation to their utility is their lack of adaptability. DSPs are a combination of hardware and software that allow the operation and functionality of a chip to be constantly changed. If new features or computations need to be completed, a new software program can be loaded into the DSP on the fly. If a change to an ASIC is desired, a new silicon chip must be designed and manufactured. Thus there are large financial and time impediments limiting the flexibility of ASIC design. In a related application, DSP cores are sometimes used within ASICs, creating custom DSP-based chips with specific functionality.

## C. Traditional processors

General-Purpose Multiprocessors (GPP) are optimized to run entire systems, such as a desktop computer, and thus must be able to complete many different tasks, most of which are unnecessary for dedicated signal processing. They are large chips that dissipate a lot of power. DSPs are optimized for the completion of relatively few tasks many times in succession. Thus their entire architecture is customized to this functionality and results in significant performance increases over GPPs. For example, DSPs can complete multiple arithmetic functions within a single cycle. In fact, current DSPs execute up to eight operations within one clock cycle. Additionally, customized addressing modes as well as parallel memory access capabilities enhance the performance of a DSP. GPPs are typically not well-suited for the computationally intensive roles served by DSPs.

## VI. GENERAL CITATIONS

Portions of this paper were inspired by [4], [5], [6], and [7].

#### REFERENCES

- [1] S. W. Smith, *The Scientist and Engineer's Guide to Digital Signal Processing*. California Technical Publishing, 1997.

- [2] (2004) Bores signal processing introduction to dsp. [Online]. Available: http://www.bores.com/courses/intro/

- [3] (2001) Ee times: Dsps. [Online]. Available: http://www.eetimes.com/story/OEG20010604S0057

- [4] (2002) Comp.dsp faq: Dsp chips. [Online]. Available: http://www.bdti.com/faq/3.htm

- [5] Howstuffworks inside a digital cell phone. [Online]. Available: http://electronics.howstuffworks.com/inside-cell-phone.htm

- [6] (2004) multimedia phones. [Online]. Available: http://www.1st-in-cellphones.com/21797-multimedia-phones.html

- [7] (2004) Getting started : What is dsp? [Online]. Available: http://dspvillage.ti.com/docs/catalog/dspplatform/details.jhtml?templateId=5121 &path=templatedata/cm/dspdetail/data/vil\_getstd\_whatis

## FPGA Architecture, Algorithms, and Applications

Kathleen King and Sarah Zwicker Franklin W. Olin College of Engineering Needham, Massachusetts 02492 Email: {kathleen.king, sarah.zwicker}@students.olin.edu

Abstract—FPGAs are reconfigurable devices that have received much attention for their ability to exploit parallelism in algorithms to produce speedup. The reasons for their success lie in the architecture of the FPGA, the algorithms involved in programming FPGAs, and the type of the program being run on the FPGA. This paper presents an overview of the development of the current FPGA architecture, the algorithms that have been developed to automate the process of programming FPGAs, and the common reasons for speedup in applications.

### I. INTRODUCTION

Field Programmable Gate Arrays (FPGAs) belong to the family of reconfigurable devices. A reconfigurable device is a piece of hardware that can be customized easily, often making it faster than regular computer processors and more flexible to change than hardwired circuits. Application-Specific Integrated Circuits (ASICs) are hardwired circuits that can be used to provide efficient solutions to very specific problems. It is difficult and time consuming to design and produce an ASIC, even though once the machinery is in place to produce one, millions more can be made easily. They are thus excellent solutions when mass production is required or when execution speed is desirable at any cost. Processors, on the other hand, are affordable and extremely flexible; they can do many different jobs using the same hardware. Unfortunately, processors are also much slower than ASICs because they are not optimized for any particular task. Thus, it is really unsurprising that reconfigurable devices like FPGAs have become very popular in recent years; they fill the gap between these two popular devices [1].

This paper attempts to explain to an audience of computer architecture students what FPGAs are, why they have the architecture they do and what they are good at. An overview of FPGAs in the context of other reconfigurable devices is given to provide context. Then, the advantages and disadvantages of using various control technologies are considered. The FPGA architecture section discusses the development of the current 4-LUT-based island-style architecture. Next, the process of programming an FPGA is examined, including automated software algorithms that have been developed. Finally some current applications of FPGAs are explored.

#### **II. RECONFIGURABLE DEVICES**

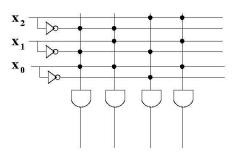

Reconfigurable devices consist of arrays of gates connected by a network of wires and switches. Opening or closing the switches controls the behavior of the circuit. The simplest of these devices is the Programmable Logic Array (PLA), which

Fig. 1. A Programmable Logic Array

can easily be used to emulate any truth table. PLAs connect a set of inputs to an array of switches. These switches select inputs and send them to various AND gates, whose outputs can then be selected by another set of switches to be delivered to a column of OR gates. A sample PLA is shown in Figure 1. A Programmable Array Logic (PAL) is sometimes defined exactly the same as a PLA, but other times it is specified that the outputs of a PAL may be connected back to the device as inputs, which is not allowed in PLAs.

PLAs and PALs devices are the simplest type of reconfigurable devices. One step above these arrays is the Generic Array Logic (GAL), which is similar to a PAL, except the output of each OR gate of a GAL feeds directly into an output logic macro cell. Each of these cells contains a D-flip-flop and so has the option of acting as a state holding element.

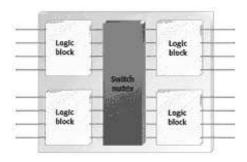

All of the devices discussed thus far fall under the category of Programmable Logic Devices (PLDs). While they may too simple to be widely useful, they are extremely inexpensive and easy to use so they are still commercially available and quite common. However, for more complicated functions, none of these simple pieces of logic are sufficient so Complex Programmable Logic Devices (CPLDs) were developed. A CPLD is a collection of PLDs along with a switch matrix, which is a set of wires with programmable switches that give the user greater flexibility, as shown in Figure 2.

However, CPLDs also have limited functionality, since the switch matrix is not usually large enough to be capable of connecting any two logic blocks. As more PLDs, wires, and switches are added to the CPLD, it eventually becomes an FPGA [2]. FPGAs can be used to replicate almost any kind of hardware, including full processors, although not every function takes advantage of the FPGAs unique abilities. Applications of FPGAs will be discussed in a later section of

Fig. 2. A Complex Programmable Logic Device

this paper. First the architecture and programming of an FPGA shall be considered.

### III. FPGA CONTROL TECHNOLOGY

The function of the FPGA chip is programmed by controlling millions of switches. The technology chosen for these switches has the potential to greatly enhance or detract from the efficiency of the FPGA. One early switching method was to use Erasable Programmable Read-Only Memory (EPROM). EPROM, once programmed, remains so for up to twenty years, unless it is exposed to intense ultraviolet light. It does not require any power source to retain its programming. However, it is significantly slower than other forms of memory, so it has become obsolete in modern FPGAs.

The most common form of control in commercial FPGAs is Static Random Access Memory (SRAM). SRAM is composed of several transistors which form two inverters that have two stable states, which correspond to 0 and 1. However, SRAM requires a continuous power supply in order to retain its state, although unlike dynamic RAM, which uses a capacitor to maintain its value, SRAM does not need to be refreshed periodically. The main advantages of SRAM are that it is extremely fast and very easy to reprogram; when its power is turned off, its memory is erased. Of course, these values can be saved off-chip on a non-volatile type of memory and reloaded when power is restored to the FPGA [4].

Antifuses are the other form of control still in use, although they are far less common than SRAM. Antifuses have very high resistance, so when they are placed between wires they stop current from flowing, acting as an open switch. When programming an antifuse-based FPGA, a high voltage is sent through the antifuses that need to act as closed switches. This causes the fuse to "blow", creating a low resistance path that allows current to flow. One obvious disadvantage of antifuse FPGAs is that they are not reprogrammable [4].

This may seem to defeat the entire purpose of an FPGA, but they still fill a special niche in the market. First of all, antifuse-based boards are faster even than SRAM, since once they have been programmed the FPGAs are essentially hardwired circuits; there are no switches to delay signals. Also, while it may be necessary to pay \$100 to replace an FPGA board after one discovers that a mistake has been made in its programming, \$100 is far less than the millions of dollars

Fig. 3. An Island-Style FPGA Architecture

necessary to fabricate a new ASIC. Finally, and perhaps most importantly, antifuses are not subject to damage from cosmic rays. Cosmic rays are capable of interfering with transistors, the building blocks of SRAM, which means that they can cause an SRAM bit to suddenly change from a 0 to a 1, or vice versa. Under normal circumstances, this is not a major concern; SRAM FPGAs can be shielded, and on earth cosmic ray interference is fairly uncommon. However, FPGAs are often used in space, where heavy shielding is an unpractical expense and there is no atmosphere to protect devices from cosmic rays. Thus, antifuse FPGAs offer a fitting solution, since cosmic rays have no effect on them.

However, despite the utility of antifuses in specialized realms, SRAM FPGAs are almost universally used in terrestrial applications. Therefore, throughout the remainder of this paper it shall be assumed that SRAM is used for the switches otherwise explicitly stated.

#### **IV. FPGA ARCHITECTURE**

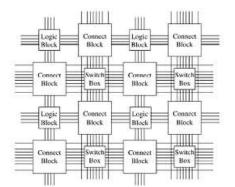

Architecturally, the essential ingredients of FPGAs are logic blocks and a routing network that connects the logic blocks. The logic blocks may each contain some sort of PLD and possibly some small amount of memory. They are laid out in a regular pattern over the FPGA chip. This can be done in a variety of ways, but the most common is an island style, where islands of logic blocks float in a sea of routing wires and switches, as shown in Figure 3. There are also other types of islands in the sea, called connection blocks and switch blocks. Switch blocks allow signals to be passed off onto different wires. Connection blocks control what signals are sent in to logic blocks as inputs and what signals are accepted as outputs. These will be discussed in greater detail later [1].

First, logic blocks will be considered. The goal in designing FPGAs is to use the minimum amount of area used by the logic blocks while minimizing delays, thereby making the circuit as fast and efficient as possible. Numerous studies have been done, mostly in the early development of FPGAs, to determine the optimal size of a logic block. Size, in this case, is talked about as corresponding to the amount of work that the block can do. The size of the logic blocks on a chip is described as its granularity. Small blocks are said to be fine-grained, while

larger blocks are more coarse-grained. Some extremely finegrained logic blocks used in early FPGAs contained as little as several transistors, while extremely coarse-grained blocks might have all the functionality of a full ALU. FPGAs that are homogeneous with only one extreme grain size are now obsolete. Fine-grained logic blocks require too many wires and switches and routing is a primary cause of delay in FPGAs. Exceedingly coarse-grained blocks lead to faster FPGAs on some occasions, but they minimize the overall flexibility of the device [4].

Thus, logic block sizes falling somewhere between these extremes were destined to become the popular choice. Mediumgrained logic blocks can be based on one of three ideas. The blocks could contain arrays of simple gates, making them virtually identical to PALs or GALs. These blocks have a great deal of flexibility, but it is difficult to take full advantage of all the available gates, so this design for a logic block ends up wasting significant amounts of space. Multiplexers and Look-Up Tables (LUTs) offer other possible solutions [4].

A LUT is in essence a piece of SRAM. The inputs to a LUT give the address where the desired value is stored. For a particular boolean function, a LUT can be made by storing the correct outputs in the slots to which the inputs point. Thus, LUTs can output in a single step for any number of inputs, while multiplexers require  $log_2(n)$  steps for an *n*-input function. Clearly, LUTs work more efficiently than multiplexers. Therefore current logic blocks are based on LUTs in order to minimize delay and avoid wasting space. LUTs may have any number of inputs, leading to logic blocks of anywhere from medium to very coarse granularity. The optimum size of logic blocks has been determined experimentally. One particularly important paper was [5], which will now be reviewed briefly.

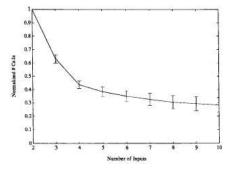

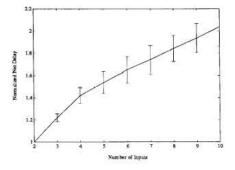

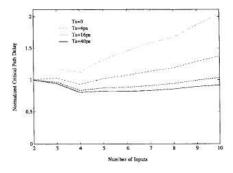

Logic blocks with one input and some number, K, outputs were tested on various benchmark circuits implemented on FPGAs. Figures 4, 5, and 6 show the results of these experiments for various numbers of inputs, assuming different switch delays,  $\tau_s$ . Recall that switch delays are the result of switch choice; that is, whether control is performed with SRAM, antifuses, or EPROM determines the switch delay. Since modern FPGAs almost universally use SRAM, this element of the results presented is obsolete.

Figure 4 shows that if blocks with more inputs are used, then a smaller total number blocks is necessary, with a sharp decrease until K = 4 and flattening after that point. However, Figure 5 shows that blocks with more inputs have significantly greater associated delay per block, which is to be expected since more inputs require more routing. Figure 6 surprisingly shows that the total path delay per block had a local or absolute minimum at K = 4. Thus, [5] concludes that 4, or possibly 5, input logic blocks are optimal for performance.

One may get a sense from this research, which shows that 4-input logic blocks are preferable, and the discussion above, in which it was decided that logic blocks based on LUTs are optimal, that 4-LUTs are the best choice for LUTs. Others have done more research and confirmed that 4-LUTs are indeed best for optimizing both speed and area of FPGAs, as is

Fig. 4. Number of Logic Blocks, for Blocks with K Inputs

Fig. 5. Delay per Block, for Blocks with K Inputs

discussed in [4]. In fact, 4-LUTs remain the industry standard for FPGAs, although it is no longer universally accepted that 4-inputs are ideal for every logic block.

More recent papers, such as [6], have discovered that sometimes grouping several connected 4-LUTs into a single logic block minimizes delays and area. The idea behind [6] is that hardwired connections eliminate switches, which take up space and delay signals. Through experimentation similar to [5], it was discovered hardwiring four 4-LUTs in a particular tree structure maximizes the efficiency of a logic block.

Of course, logic blocks are not the only part of an FPGA which may be improved. In fact, most modern research is directed toward optimizing the routing of wires between logic

Fig. 6. Total Path Delay, for Blocks with K Inputs

blocks. Since only ten percent of an FPGA's area is used for logic while ninety percent is used for routing, this focus is not surprising [1]. Since routing also has the potential to cause a great deal of delay, many people work on trying to find ways to place wires efficiently to minimize both area and delay. The research done in [6] addressed this problem by attempting to determine the best lengths of wires. Adding switches to the network of wires allows for greater flexibility, but switches cause delays and take up space. However, while long wires are faster, if they are not necessary then they waste area. In [6], it was determined that it is preferable to have 56 percent of wires be short, 25 percent medium, and 19 percent long.

The routing research example describes a very high-level architectural decision. However, knowing that architectural features of FPGAs is only a starting point. To actually implement a circuit on an FPGA requires that the logic blocks be arranged on the board and connected with wires. These tasks are extremely difficult to perform, and currently much research is being done to determine the best methods of doing them. The next sections of this paper shall present common algorithms used in implementing programs on FPGAs.

## V. SOFTWARE

There are currently many automatic software solutions capable of taking high level code, designing the corresponding logic blocks and wiring scheme, for downloading to an FPGA. The following section discusses the process by which software algorithms perform these tasks. First, it is necessary to have code that describes a list of connections between logic gates in a low-level language like Verilog. The automated process begins with the technology mapping of the designer's code. The technology mapping process takes the code and translates it into a netlist of logic blocks specific to the FPGA. Often circuit libraries, which contain the logic-block-based structures of commonly used elements, such as adders and multipliers are used to facilitate this process. Also at this stage, if the system contains more than one FPGA, the netlist is partitioned into the parts that will go on each FPGA.

Next, a placement algorithm is used to assign the netlist of logic blocs to specific locations on the FPGA. Floorplanning, or the grouping of highly connected logic blocks into particular regions on the FPGA, can help the placement algorithm to achieve a reasonable solution. Often the placement algorithm is based on simulated annealing, a heuristic process that can be run until a desired goal is reached. The goal of the placement algorithm is closely tied to the next step in the automated process, which is routing. Better placement means that wires will need to be routed through fewer connections, or switches, making the circuit run faster.

After placement is complete, the layout and netlist are used to route the wires, or signals, through the FPGA. Routing is limited by the fact that there is a specific number of wires that can be connected to each logic block and that can run in the channels between the logic block islands of the FPGA. Thus, the routing algorithms have to work within that constraint to find a good scheme. Routing has the most direct affect on the performance of the circuit; if there were inefficiencies in earlier processes, they increase delays in routing. Once routing is complete, a translation of the logic block and connection layout information can be easily created and downloaded onto the FPGA.

In the early days of FPGAs, placement and routing were done by hand, as was the individually programming each LUT and multiplexer. Manual circuit description is a timeconsuming process and requires low-level customization for specific architectures. It can produce high-quality circuits in terms of algorithm speedups and exploited parallelism. However, as the FPGA has grown in number of logic blocks and routing wires, it has become increasingly convenient to have automated design tools available to do mapping, placement and routing.

## A. Technology Mapping

Technology mapping converts code into circuit components based on the architecture of the logic blocks in the FPGA. If the code is high level like Java or C, it will need to be processed into a netlist. However, if it is low level such as Verilog or VHDL, it can be run through a technology map algorithm directly. As an example of technology mapping, if the FPGA hardware was composed of logic blocks containing 4-LUTs, some logic functions in the code that had more than 4 inputs would have to be spread over multiple logic blocks. Technology mapping algorithms can try to minimize the number of logic blocks used or optimize for routeability. Routing is made more complex by the increasing heterogeneity of commercial FPGAs, meaning that they involve a variety of sizes and types of logic blocks.

Because each FPGA may have different types of logic blocks arrayed in unique layouts, it has become the standard for FPGA manufacturers to offer circuit libraries. Circuit libraries incorporate low level details into an abstraction of common components such as adders and multipliers. In this way, common components can be designed and optimized by those who have specialized knowledge of their specific FPGA architecture. The FPGA can then be programmed from a higher level. The abstractions of these tools are generally architecture independent so that once a user learns how to program one FPGA, he does not need to spend time learning how to use the tools for another type.

Technology mapping can include more than one FPGA, in which case the netlist must first undergo a process called partitioning. Manual partitioning of pieces of the netlist can yeild highly optimized layouts. However, it is sometimes time consuming and complex. To address this problem, [7] discusses a method for automatically partitioning netlists for a variety of FPGA architectures. The best partitions have the fewest interconnections that have to run between different FPGAs. Finding the best partition is the NP-hard mincut problem. The algorithm presented in [7] attempts to solve the mincut problem heuristically.

## B. Placement

After the logic blocks and their connections have been mapped, the logic blocks are placed on the FPGA board. Placement has also been shown to be an NP-hard problem. An intermediate step that can facilitate the placement process is a global placement or floorplanning. The floorplanning algorithm groups highly-connected components into clusters of logic cells and places these onto bounded regions of the FPGA board [1]. Also, macros, or repeated data paths, in circuits can be laid out as single units in their own regions. The placement algorithms can then be used to configure logic blocks within each region.

The most common placement algorithm is based on a simulated annealing as described in [8]. The metallurgical definition of annealing involves heating up a material, usually a metal, to allow the atoms to move. The atoms are capable of moving greater distances at higher temperatures. At higher energy states, dislocations begin to disappear and grains begin to grow, giving the desired effect of making the material more ductile. In simulated annealing, an initial placement of 'atoms' (in this case logic blocks) is chosen and modified through repeated cycles until an acceptable solution is reached. The cycles begin with a 'high energy state,' in which random logic blocks are allowed to swap places. For each potential switch, a cost function is used to estimate how good or bad this swap will be. As each cycle progresses, the threshold is raised for how good a swap has to be in order to be allowed. The annealing technique helps avoid local minima (as often occur in a greedy algorithm) by sometimes allowing swaps that do not have good cost values. Just as the cooling schedule is important in determining the ductility of a metal, the cooling schedule of the simulated annealing cycle is an important factor in the success of the algorithm at obtaining a good placement. Therefore, the annealing procedure is often timeconsuming, on the order of hours [10].

Also important to the simulated annealing algorithm is the accuracy of the cost function in determining good choices. At this point, it can only be estimated how the logic blocks will be routed, and the estimates have to be decided quickly. One of the challenges of automating FPGA programming is that placement and routing are both NP hard problems. Thus, it is not surprising that a good algorithm that considers both problems at once has not yet been found. The flexibility of the resources of the board is also important. If too much of the board is in use, the algorithm may not be able to find an acceptable solution. The factors that affect flexibility include the architecture of the FPGA and the amount of the board that is in use.

## C. Routing

Once placement of the logic blocks has been done, routing will determine which wires and switches, or nodes, to use for each signal. FPGA routing is fundamentally different from ASIC routing because the wires and connection points are limited, which means that global and local routing need to be done simultaneously. This and other distinctions make research done on ASIC routing of little use in helping to determine FPGA routing. The basic routing problem tries to minimize path length by minimizing the use of routing resources, while simultaneously trying to minimize delay. However, minimizing delay often requires taking longer but less congested paths.

One approach to minimizing delay is to attempt the routing of the entire FPGA and then search for areas that are not optimal. At these areas, 'rip-up and retry;' that is, remove all of the wires and try to find a better local routing. The success of this method is highly order dependent: if the program does not start with a good node to optimize from, it will get stuck in a local minimum. Many software applications use the PathFinder, which is an iterative algorithm that allows signals to pick their preferred path and then negotiate with other signals for resources. During the first iteration, the signals are treated as independent with each node only costing its intrinsic delay. During subsequent iterations, the history of congestion is added into the cost of each node. This cost is multiplied by the number of signals using the node. Thus, signals that are sharing the same node in the most direct path gradually decide to use less congested nodes. Also, because of the history term, the cost of using congested nodes is permanently increased so paths that move off of congested nodes do not try to return. If the history term does not exceed the intrinsic delay, then the algorithm that PathFinder uses for negotiating congestion and delay routing has been proven to achieve the fastest implementation for the placement. In practice, the history term will exceed the intrinsic delay for very congested circuits, but even then, results are close to optimal [11].

All of these software algorithms facilitate the generation of efficient designs in a shorter time span than it would take to hand-map the program onto a modern FPGA. It is now possible to implement specific applications and utilize the qualities of the FPGA to achieve speedup on common programs.

#### VI. APPLICATIONS

In general, FPGAs are good at applications that involve rapid prototyping of circuits, algorithm acceleration, and multiple processors, when the FPGA works alongside a CPU. Image processing is generally a good candidate for FPGAs because of the high level of fine-grain parallelism they can support. The ability of FPGAs to act as coprocessors makes them desirable for use in satellites. FPGAs can perform such functions as image compression for the CPU and also serve as a backup in case of problems.

One example of an application that took advantage of the computing power of FPGAs is a genetic algorithm used to solve the traveling salesman problem in [12]. Using a system of four FPGAs, an execution time speedup factor of four was achieved, compared to a software implementation of the same problem. Fine-grain parallelism accounted for more than a 38X overall speedup factor. Hard-wired control intrinsic to the FPGA hardware accounted for an overall speedup

factor of 3X. There was also some speedup due to coarsegrain parallelism and random number generation. Parallelism in FPGAs often accounts for their speedup over software algorithms; however the algorithm used in this case was not "embarrassingly parallel" as are some hardware design, which showed that FPGAs are valuable beyond their parallelism.

Many applications of FPGAs for algorithm acceleration have been found in the field of cryptography. For example, a certain process called sieving is used to factoring large numbers in the fastest published algorithms for breaking the public key cryptosystem designed by Rivest, Shamir and Adleman (RSA). [13] used an FPGA system to get a speedup of over 28X compared to the more traditional UltraSPARC Workstation running at 16 MHz. They estimate that an upgrade to FPGAs using 8ns SRAM will give a speedup factor of 160. If this change were made, theoretically the only two months would be required to break RSA-129 (the RSA encryption using 129 digit primes).

### VII. SUMMARY

This paper has attempted to present an overview of FPGAs at a level accessible to undergraduate engineering students. It has discussed where FPGAs fit into the family of reconfigurable devices and explained why SRAM is most commonly used in FPGA switches. The common island style architecture has been examined and the tradeoffs between space for logic blocks and routing considered. The development of 4-LUTs as the prominent element in logic blocks was discussed. Algorithms that perform mapping, placement, and routing on FPGAs were explained. Finally some applications that have witnessed significant speedup due to FPGA use were discussed, along with the reasons for the speedup. Thus, this paper has given a broad survey of the architecture, algorithms, and applications of FPGAs.

### ACKNOWLEDGMENT

The authors would like to thank Mark Chang for his extensive help with the research for this paper. The authors would also like thank Sean Munson and Clara Cho for their generous commitment of time and camaraderie.

#### REFERENCES

- K. Compton and S. Hauck, "Reconfigurable Computing: A Survey of Systems and Software," ACM Computing Surveys, vol. 34, no. 2, June 2002, pp. 171-210.

- [2] M. Barr, "How Programmable Logic Workds," *Netrino Publications*, url: http://www.netrino.com/Articles/ProgrammableLogic, 1999.

- [3] B. Arbaugh and M. Hugue, *Programmable Logic array*, Computer Organization Notes, Dept. Comp. Sci., Univ. Maryland, url: http://www.cs.umd.edu/class/spring2003/cmsc311/Notes/Comb/pla.html 2003.

- [4] J. Rose, A. El Gamal, and A. Sangiovanni-Vincentelli, "Architecture of Field-Programmable Gate Arrays," *Proc. of the IEEE*, vol. 81, no. 7, July 1993, pp. 1013-1029.

- [5] J. L. Kouloheris and A. El Gamal, "FPGA Performance versus Cell Granularity," *Proc. Custom Integrated Circuits Conference*, 1991, pp 6.2.1-6.2.4.

- [6] P. Chow, S. O. Seo, J. Rose, K. Chung, G. Páez-Monzón, and I. Rahardja, "The Design of an SRAM-Based Field-Programmable Gate Array - Part I: Architecture," *IEEE Transactions On Very Large Scale Integration Systems*, vol. 7, no. 2, June 1999, pp. 191-197.

- [7] U. Ober and M. Glesner, Multiway Netlist Partitioning onto FPGA-based Board Architectures, IEEE Proc. Conf. on European Design Automation, 1995.

- [8] S. Kirkpatrick, C. D. Gelatt, and M. P. Vechi, "Optimization by Simulated Annealing," *Science*, vol. 220, no. 4598, May 1983.

- [9] M. L. Chang, Variable Precision Analysis for FPGA Synthesis, Ph.D. Dissertation, Dept. Elect. Eng., Univ. Washington, 2004.

- [10] S. Hauck, *Multi-FPGA Systems*, Ph.D. Dissertation, Dept. Comp. Sci. and Eng., Univ. Washington, Sept. 1995, pp. 36-42.

- [11] L. McMurchie and C. Ebeling, "PathFinder: A Negotiation-Based Performance-Driven Router for FPGAs," ACM/SIGDA International Symposium on Field Programmable Gate Arrays, 1995, pp. 111-117.

- [12] P. Graham and B. Nelson, "Genetic Algorithms in Software and in Hardware - a Performance Analysis of Workstation and Custom Computing Machine Implementations," *IEEE Symposium on FPGAs for Custom Computing Machines*, 1996.

- [13] H. J. Kim and W. H. Mangione-Smith, "Factoring Large Numbers with Programmable Hardware," ACM/SIGDA Int'l. Symp. on FPGAs, 2000.

## A History of Nintendo Architecture

Jesus Fernandez, Steve Shannon

*Abstract*— The video game industry shakedown of 1983 seemed to be the end of the industry in the States. In spite of this, it is at this time that Nintendo released the NES as an astronomical success for the company. The architectures of the NES, SNES and N64 systems are not only influenced by the ambitions of Nintendo's engineers, but also from external circumstances like economic climate, business partnerships, and marketing.

*Index Terms*— Nintendo, NES, SNES, N64, Computer Architecture, Console Design

### I. INTRODUCTION

THE year is 1983. Atari has declared bankruptcy after reporting a loss of over \$500 million from the failed releases of *E.T.* and *Pacman* for the Atari 2600. The economy itself is in a slump. The bottom has fallen out of the video game market, and the public as a whole has all but renounced the console system in favor of the emerging personal computer. From this description, one would think that introducing another new console only two years later would be the quickest form of corporate suicide. However, that's just what Hiroshi Yamauchi, Masayuki Uemura, and the engineers of Nintendo did, and through a series of intelligent marketing and business decisions, the "big N" single-handedly revitalized and redefined the video game industry as they saw fit.

Not surprisingly, the decisions that led to the success of Nintendo's first mass-market system played a direct role in how the system's infrastructure was designed. Then, as the industry grew back steadily and the pertaining technology caught on, competitors immerged once more. Nintendo had to keep evolving with the market in order to stay competitive, which meant updating its design and system capabilities. In addition, Nintendo's constant desire to push the limit of the industry and be the innovator had significant impact on the infrastructure as years went on.

## II. NINTENDO ENTERTAINMENT SYSTEM

The Nintendo Entertainment System (NES) – known as the Famicom in Japan – was first envisioned by Yamauchi to be a 16-bit console selling at a street price of \$75 dollars. The goal

was clear: to develop an inexpensive system that would be better than its competitors' offerings. While Yamauchi was able to secure some fairly advantageous deals with semiconductor companies and distributors, many decisions had to be made to cut costs in the system's design. Many desired "extras" like keyboards and modems were dropped completely despite being implemented in the hardware itself. [1]

Later on, the video game industry shakedown of 1983 also had an effect on the design of the system Nintendo would release in the US. Most noticeably, the look and feel of the system was changed so that it would not remind consumers of other home consoles which had fallen out of style in the States. More importantly –however – was the development of a "Lockout" circuit that prevented the running of unlicensed code, giving Nintendo control of the distribution of games on its console. This measure would prevent any future oversaturation of the video game market for the Nintendo console.

The Nintendo Entertainment System was released in the US in 1985 at a price of approximately \$200 with the following technical specifications:

- 2A03 CPU a Modified MOS 6502 8-bit processor with 5 sound channels and a DMA controller on-chip clocked at ~1.79Mhz

- 2C02 PPU Picture Processing Unit

- Main RAM: 2KB

- Video memory: PPU contains 2 KB of tile and attribute RAM, 256 bytes of sprite position RAM ("OAM"), and 28 bytes of palette RAM

From these specifications it is possible to see where Nintendo's engineers were able to cut costs within the design of the system. The MOS 6502 was not only less expensive than other processors at the time, but it also outperformed them. Integrating the MOS 6502 and a sound generating unit into the 2A03 made it so that there would need to be fewer independent components on the NES' mainboard to manage using costly "glue logic".

## Fig 1. The MOS 6502. [3]

The MOS 6502 is an 8-bit pipelined processor with a 16-bit address bus and an 8-bit two-way data bus. It also had an 8-bit ALU as well as the following internal registers:

- Two 8-bit index registers (X and Y)

- One 8-bit stack pointer register (SP)

- One 8-bit accumulator index (A)

- One 16-bit program counter register (PC)

- One 8-bit processor status register (SR)

There were no internal data registers, since it was optimized for RAM access – which at the time, was much faster than the CPU. [2]

Each of the MOS 6502's instructions makes use of one of 13 addressing modes that effectively used each of the internal data registers on the chip. Since the 16-bit address bus is split into two 8-bit buses, these addressing modes make it easy to traverse different "pages" – defined by the high 8 bits – of memory each representing a different 8-bit address space.

There are a set of addressing modes that implicitly direct to the  $0^{th}$  page of memory, which in most MOS 6502 programs becomes a sort of register.

Nintendo made some modifications to the MOS 6502 in creating the 2A03. The MOS 6502's decimal mode was disabled in the 2A03. Additional features connected to the CPU through specific addresses, giving it access to the sound hardware on the 2A03, the 2C03's VRAM, the ROM and RAM on the cartridge, joysticks and other hardware.

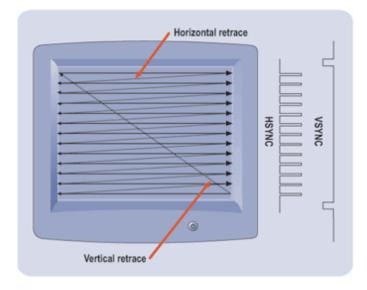

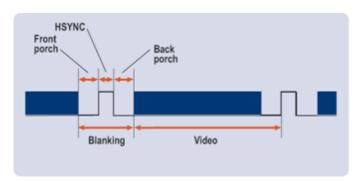

The 2C02 was a Picture Processing Unit capable of producing 256x240 color video signals on a television set one scan-line at a time. It has a palette of 48 colors and 5 shades of grey, but only 25 would be visible on a given scan-line at a time. Additional colors could be "created" by the PPU's ability to dim the red, green, or blue value on any given scan-line. The CPU would write to the PPU's VRAM during "Blanks", periods of time during which it was guaranteed that the PPU would not be accessing its VRAM.

In the NES, it was responsible for drawing the playfield as well as the interactive objects in the screen. Additionally it was capable of detecting collisions between objects in the image and report those back to the CPU. Images were drawn on the screen in 8x8 or 8x16 blocks using colors defined in 4color palettes all defined in cartridge ROM.

The PPU was capable of 4-directional scrolling. Advanced techniques such as parallax scrolling and split-screen scrolling could be done on the NES but it requires cycle-timed code and accesses to the PPU VRAM outside of the Blank period to implement.

## III. SUPER NES

The wild success of the NES made it practically the only choice for home video gaming, completely marginalizing competing consoles, and Nintendo's licensing practices – while almost draconian in the degree of oversight the company had over its third-party publishes – still managed to exclusively secure the best programming talent of the day. That is until new competition arrived in the form of the Sega Genesis in 1988. While not interested in developing a new console to compete with the Genesis, it became evident that Nintendo had to act to be able to compete with the Genesis' superior technology.

Their response was the Super NES (SNES), released in 1990, essentially an evolution of the NES architecture, the SNES was considered at the time to be nearly flawless, boasting a slick new graphics chip, a Sony-designed proprietary sound chip, and several hardware modes that allowed for complex manipulations of sprites to simulate 3D graphics. Indeed, the only qualms that many had with the SNES was that it had a rather sluggish main CPU. However, when push came to shove, the SNES was able to outperform the Genesis in almost every way, and it was indicated that the SNES had outsold the Genesis by about one million units by 1996.

The controversial CPU was the MOS 65c816, a 16-bit version of the MOS 6502 found in the NES. It was able to run in an 8-bit emulation mode as well as the 16-bit native mode, making it almost 100% compatible with the 6502, but it was clocked at an unimpressive 2.68-3.58 MHz (compared to the 7.61 MHz M68000 processor running in the Genesis). Though Nintendo later found ways to get around this crater by incorporating additional chips into the game cartridges themselves, the real stars of the show were the graphics and sound co-processors, providing the power and performance that tipped the market scales in Nintendo's favor.

The graphics chip had several different hardware modes builtin that performed complex calculations automatically:

• Rotation: On the NES, in order to perform a smooth rotation on a sprite you had to construct an animation consisting of a large number of frames. The more frames used, the smoother the rotation appeared, but also the more memory required to store the costly

animation. The Rotation Mode on the SNES graphics chip allowed it to rotate sprites on the fly in realtime without any need for animation frames.

- Scaling: Resizing sprites on the NES also necessitated the use of a multi-frame animation being stored in memory. The Scaling Mode did all the scaling animation in realtime, allowing games to simulate the "nearness" and "farness" of 3D distances in a 2D environment.

- Transparency: An effect not even conceptualized for the NES, the Transparency Mode could make sprites and backgrounds appear transparent or translucent, allowing for amazing new elemental effects like water, fire, smoke, and fog.

- Mode 7: The most famous of the SNES hardware modes, the evolutionary Mode 7 made it possible to scale and rotate large backgrounds to simulate 3D environmental illusions, such as flying over a large terrain in a plane.

These hardware modes, coupled with the ability to simultaneously display 256 colors from a palette of 32768, let the SNES quickly and effortlessly push advanced, 3D-like graphics to the screen that were vibrant and colorful, whereas the Sega Genesis was often defamed for its often grainy and drab-looking displays.

The SPC700 sound chip was capable of handling 44 KHz worth of sound data on 8 channels, and it had 64 Kb of dedicated memory. However, its truly ground-breaking aspect was the inclusion of the first Wavetable MIDI synthesizer ever to appear on a console, meaning it could play "sampled" sound from a generous selection of built-in MIDI instruments. Compared to the poor radio-quality sound on the Genesis, the SNES was in its own league. The chip was created by Sony exclusively for the SNES with the intention that they and Nintendo would partner to create a CD-ROM add-on for the main console. This deal eventually fell through though, leading to the development of Sony's own 32-bit, CD-based system called the Playstation.

## IV. NINTENDO 64

A few years passed, and gamers were expecting richer, more immersive game experiences making full use of the latest technologies available. "Multimedia" was the buzzword of the moment and companies were racing to develop the next "killer app." Developers were reaching the limits of what the Super NES could do, so a new frontier had to be explored.

That new frontier would be 3D, computer graphics have started to find their way into movies like *Jurassic Park* and consumers were hoping to have the same experience in their home video game systems. It eventually became necessary for game processors to now be able to easily compute 64-bit floating point numbers in order to handle the more complex calculations involved in drawing polygons in 3D space (instead of simulating 3D with rotating sprites). Nintendo's new system would not be an *evolution* from the Super NES, but in fact be a totally *revolutionary* new architecture. They switched from a MOS to a MIPS processor and completely redesigned the internal architecture, and thus the Nintendo 64 was born.

The emergence of the Nintendo 64, aptly named for its new 64-bit processor, helped to usher in the era of next-generation 3D graphics; it was essentially designed to (a) facilitate the programmer's transition from creating 32-bit games to creating the new 64-bit games, and (b) be as efficient as possible while dealing with the new meatier calculations and instructions.

Nintendo's most interesting decision with regards to the N64 was the fact that it was still a cartridge based system in a time when game developers and consumers were looking to CD-ROMs as the new medium for video games. CD-ROMs promised a vast amount of storage, enabling CD quality music and full motion video to be incorporated into games. CD-ROMs were also inexpensive to produce and distribute. Cartridges are more difficult and expensive to manufacture, and the expense of silicon memory chips limited the capacity to a fraction of that available on optical media.

The reason Nintendo must have chosen to go with cartridge based media lies is the speed at which data on a cartridge is made available to the N64's CPU. There is no "loading time" with cartridges. The ability to record information in oncartridge RAM is also not available on CD-ROMs.

The main processor, the MIPS R4300i, was based on the R4400 series which was a popular desktop PC processor at the time. The R4300 was configurable in both Big and Little Endean, and it was capable of running in both 32-bit and 64bit modes, containing sixty-four registers that acted as either 32- or 64-bit depending on what mode was running. It had a variable clock rate, running at about 93.75 MHz at top speed but providing several lower frequencies. Also, though it had a relatively low power dissipation to begin with (about 1.8W), it had the ability to run in a reduced power mode. All of this versatility, plus the existence of a co-processor unit that could provide additional processing power, made it a prime choice for Nintendo's new gaming system. The N64 could save on resources since not every word needed to be treated as 64-bits long. It could easily support future low-speed external addons, and it was flexible and easy to write for from the programmer's standpoint.

Half of the registers (called General Purpose Registers or GPRs) were reserved for integer operations, while the other half (called Floating Point General Purpose Registers or FGRs) were used exclusively for the floating point operations. Most of the actual calculations were performed "off-chip" by the R4300's co-processor unit which also helped to free up resources in the main CPU (plus the coder was spared the experience of having to write a bunch of messy algorithms to do all these calculations from their end).

The co-processor was a special feature of the R4300 that made it great for gaming systems. Dubbed the Reality Co-Processor (RCP) in the N64, it was the workhorse of the R4300 handling all of the memory management and most of the audio and graphics processing. The RCP was split into two sections the Signal Processor performed all 3D manipulations and audio functions, and the Drawing Processor pushed all the pixels and textures to the screen.

Another new and innovative feature of the N64 was that it incorporated a Unified Memory Architecture (UMA). This means that none of the memory was designated for any one specific purpose--the game programmer had full control over how much of the 4Mb of RAM would be allocated to what task. Additionally, the RAM could be expanded to 8Mb in order to provide even more flexibility and performance.

## V. CONCLUSION

The NES, SNES, and N64 showcase the different ways Nintendo approached the design and implementation of each of their consoles from the early 80s to the late 90s. The NES was developed carefully with an eye toward American attitudes toward video games after the industry shakedown of 1983. Nintendo aimed to recapture market share lost to the Genesis console with the SNES. The Nintendo 64 was designed to push the envelope and bring a new generation of gaming to the home with immersive 3d environments.

These and other external influences – like business partnerships, third-party developers, and economic climate – affected the architectures and technologies used in the design of each console. These systems are as much a product of the times that they were designed in as the engineering that made them possible.

#### REFERENCES

- [1] "NES History." http://www.games4nintendo.com/nes/history.php \*

- [2] "Nintendo Entertainment System."

- http://en.wikipedia.org/wiki/Nintendo\_Entertainment\_System [3] "The 6500 Microprocessor Family."

- http://6502.org/archive/datasheets/mos\_6500\_mpu\_nov\_1985.pdf [4] Regel, Julian, "Inside Nintendo 64."

- http://n64.icequake.net/mirror/www.white-tower.demon.co.uk/n64/ [5] "SNES – A Brief History of the Console."

- http://home.uchicago.edu/~thomas/xbox-history-nintendo-snes.html [6] Valta, Jouko, "65c816 Tech Sheet",

- http://members.tripod.com/FDwR/docs/65c816.txt [7] MIPS, "R4300i Product Information." http://www.mins.com/content/PressPacer/TeachLibrary/PSorie

- http://www.mips.com/content/PressRoom/TechLibrary/RSeriesDocs/content\_html/documents/R4300i%20Product%20Information.pdf

- [8] E. H. Miller, "A note on reflector arrays (Periodical style—Accepted for publication)," *IEEE Trans. Antennas Propagat.*, to be published.

- [9] J. Wang, "Fundamentals of erbium-doped fiber amplifiers arrays (Periodical style—Submitted for publication)," *IEEE J. Quantum Electron.*, submitted for publication.

- [10] C. J. Kaufman, Rocky Mountain Research Lab., Boulder, CO, private communication, May 1995.

\*This source is particularly problematic as the same text that appears on this page appears on the open internet in several locations. There did not appear to be a definitive source for this text, but it was useful for perspective into the design of the NES.

## **Graphical Processing Units: An Examination of Use and Function**

Michael Crayton Mike Foss Dan Lindquist Kevin Tostado

## Abstract

Before graphical processing units (GPUs) became commonplace on home computers, application specific processors were generally thought of as smaller market, specialty components. In the GPU, however, a processor tailored to a single purpose has become practically as ubiquitous as the CPU. Because GPUs are essentially parallel processors combined into one unit, they can outperform standard CPUs in a variety of tasks, graphics notwithstanding. Finding out how to put their specialized application to use on processor intensive problems has become a hotbed of research in the last few years, and in this paper we explore what kind of applications GPUs are being used for as well as how they function on a more fundamental level.

## **1. Introduction**

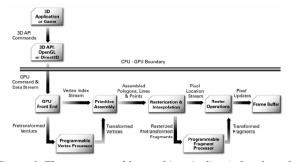

Over the past fifteen years, there have been a remarkable amount of changes in the world of computing. During that time, the general computing power of CPUs has increased dramatically. However, GPUs have improved at an even more amazing pace. Today's GPUs have more than 25 times the performance of a 3D graphics workstation of ten years ago at less than five percent of the cost. [9] As recently as 6 years ago, the graphics card simply displayed the results as a "dumb" frame buffer, and the majority of consumer 3D graphics operations were mostly calculated on the CPU. Today, pretty much any graphics functions can be delegated to the GPU, thus freeing up the CPU to do even more calculations in order to create realistic graphics. [9]

The term GPU (Graphical Processor Unit) was coined by NVIDIA in the late 1990s to more accurately describe the advancing state of graphics hardware. [10] Initially, most GPUs were connected to the CPU via a shared PCI bus. However, with 3D animation and streaming video becoming more ubiquitous, computer architects developed the Accelerated Graphics Port (AGP), a modification of the PCI bus built to help with the use of streaming video and high-performance graphics. [11]

It is generally recognized that the existing GPUs have gone through four generations of evolution. Each generation has provided better performance and a more sophisticated programming interface, as well as driving the development of the two major 3D programming interfaces, DirectX and OpenGL. DirectX is a set of interfaces developed by Microsoft including Direct3D for 3D programming. OpenGL is an open standard for 3D programming available for most platforms. [10]

The first generation of GPUs (TNT2, Rage, Voodoo3; pre 1999) was capable of rasterizing pretransformed triangles and applying one or two textures. This generation of GPUs completely relieved the CPU from updating individual pixels, but lacked the ability to perform transformations on the vertices of 3D objects. It also had a very limited set of math operations for computing the color of rasterized pixels. [10]

Before the second generation of GPUs (GeForce2, Radeon 7500, Savage3D; 1999-2000), fast vertex transformation was one of the key differentiations between PCs and high-end workstations. This generation expanded the math operations for combining textures and coloring pixels to include signed math operations and cube map textures, but was still fairly limited. The second generation was more configurable, but not fully programmable. [10]

The third generation of GPUs (GeForce 3, GeForce4 Ti, Xbox, Radeon 8500; 2001) provided vertex programmability rather than just offering more configurability. This generation of GPUs let the

application set a sequence of instructions to process vertices. There is more configurability at the pixellevel, but the GPUs were not powerful to be considered "truly programmable." [10]

The fourth and current generation of GPUs (GeForce FX family with CineFX, Radeon 9700; 2002 to present) provide both pixel-level and vertex-level programmability. This opens up the possibility of passing off complex vertex transformation and pixel-shading operations and computations from the CPU to the GPU. DirectX 9 and various OpenGL extensions take advantage of the programmability of these GPUs. [11]

Recently, graphics hardware architectures have started to shift away from traditional fixed-function pipelines to emphasize versatility. This provides new ways of programming to reconfigure the graphics pipeline. As a result, thanks to graphics chip more and more powerful general-purpose constructs are appearing in PC machines. [12]

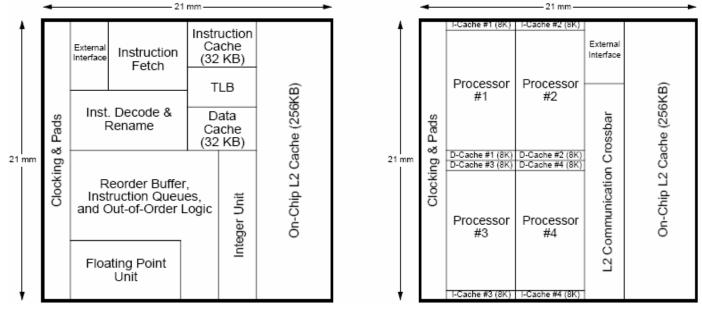

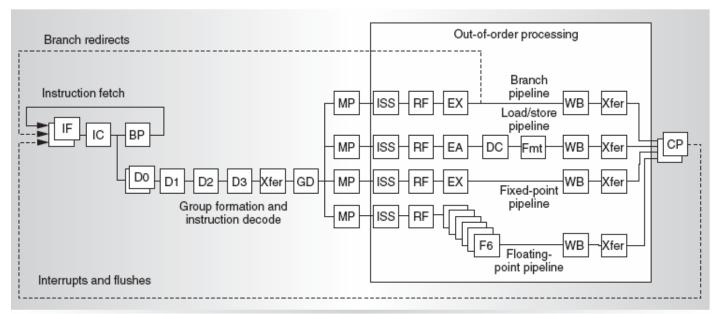

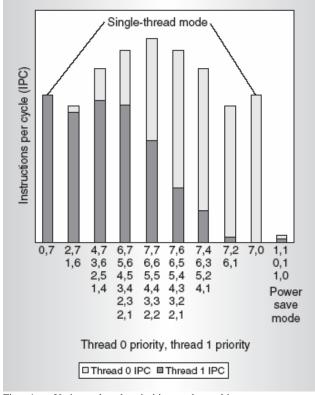

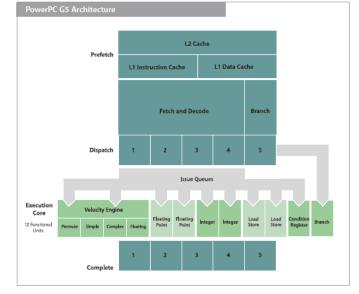

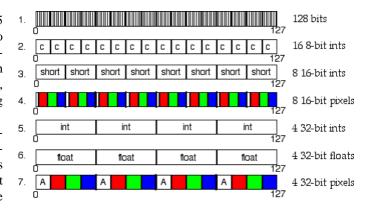

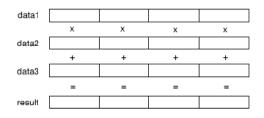

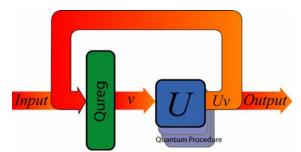

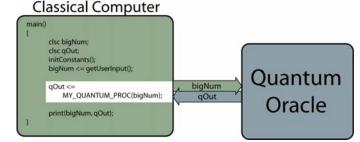

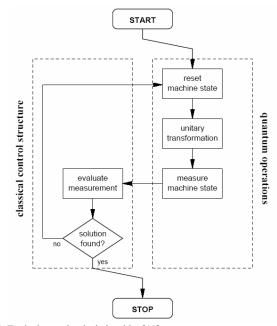

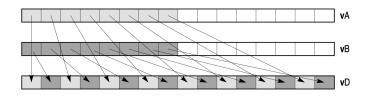

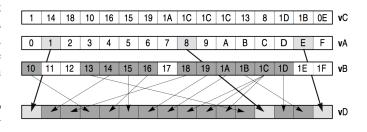

Currently, there is less time between releases of new GPUs than CPUs, and the latest GPUs also have more transistors than a Pentium IV. In the graphics hardware community, it is the general consensus that this trend will continue for the next few years. The continued development of the graphics processors will make GPUs much faster than CPUs for certain kinds of computations. [13]