Class notes based upon Patterson & Hennessy: Book & Lecture Notes Patterson's 1997 course notes (U.C. Berkeley CS 152, 1997) Tom Fountain 2000 course notes (Stanford EE182) Michael Wahl 2000 lecture notes (U. of Siegen CS 3339) Ben Dugan 2001 lecture notes (UW-CSE 378) Professor Scott Hauck lecture notes (UW EE 471) Why are you here?

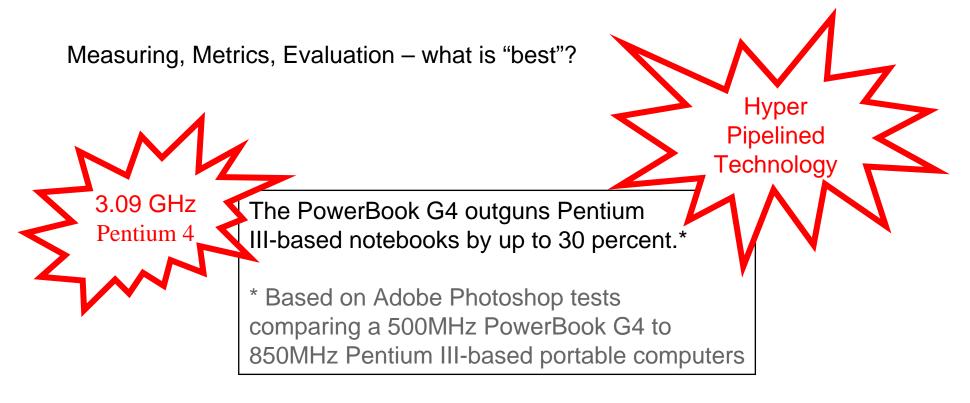

#### What things are important when buying a computer?

### **Computer "Performance"**

MIPS (Million Instructions Per Second) vs. MHz (Million Cycles Per Second)

Throughput (jobs/seconds) vs. Latency (time to complete a job)

## **Performance Example: Planes**

| Airplane     | Passenger<br>Capacity | Cruising<br>Range (miles) | Cruising<br>Speed (mph) | Passenger Throughput<br>(passengermile/hour) |

|--------------|-----------------------|---------------------------|-------------------------|----------------------------------------------|

| Boeing 777   | 375                   | 4630                      | 610                     | 228,750                                      |

| Boeing 747   | 470                   | 4150                      | 610                     | 286,700                                      |

| Concorde     | 132                   | 4000                      | 1350                    | 178,200                                      |

| Douglas DC-8 | 146                   | 8720                      | 544                     | 79,424                                       |

Which is the "best" plane?

Which gets one passenger to the destination first?

Which moves the most passengers?

Which goes the furthest?

Which is the "speediest" plane (between Seattle and NY for example)?

Latency: how fast is one person moved?

Throughput: number of people per time moved?

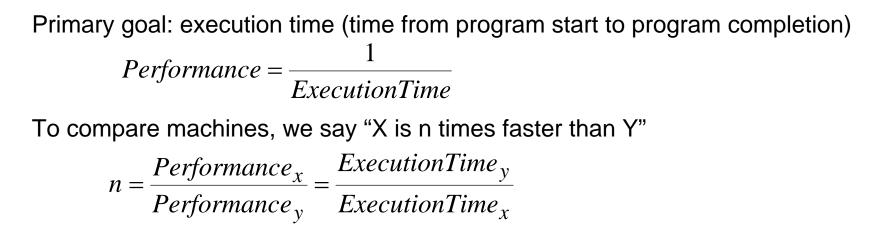

Example: Machine *Orange* and *Grape* run a program Orange takes 5 seconds, Grape takes 10 seconds

# **Execution Time**

Elapsed Time

counts everything (disk and memory accesses, I/O, etc.)

a useful number, but often not good for comparison purposes

CPU time

doesn't count I/O or time spent running other programs can be broken up into system time, and user time

Example: Unix "time" command

fpga.olin.edu> time javac CircuitViewer.java

3.370u 0.570s 0:12.44 31.6%

Our focus: user CPU time

time spent executing the lines of code that are "in" our program

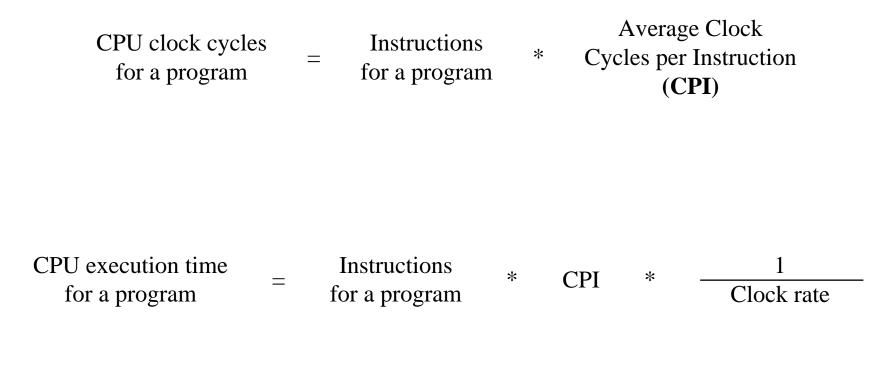

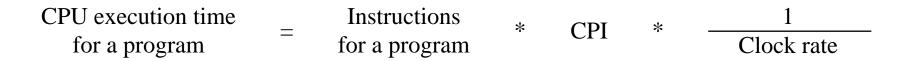

# **CPU** Time

| CPU execution time<br>for a program | = | CPU clock cycles for a program | * | Clock period    |

|-------------------------------------|---|--------------------------------|---|-----------------|

| CPU execution time for a program    | = | CPU clock cycles for a program | * | 1<br>Clock rate |

Application example:

A program takes 10 seconds on computer *Orange*, with a 400MHz clock. Our design team is developing a machine *Grape* with a much higher clock rate, but it will require 1.2 times as many clock cycles. If we want to be able to run the program in 6 second, how fast must the clock rate be?

$ORANGE 105 = \frac{x}{400}$

ERIC SEZ > 800 MHZ

How do the # of instructions in a program relate to the execution time?

# **CPI Example**

Suppose we have two implementations of the same instruction set (ISA).

For some program

Machine A has a clock cycle time of 10 ns. and a CPI of 2.0 Machine B has a clock cycle time of 20 ns. and a CPI of 1.2

What machine is faster for this program, and by how much?

CPU Clock Cycles

$$f = I \times 2.0$$

CPU Clock Cycles  $g = I \times 1.2$

(PUTIME = I x 2.0 x 10 AS = 20x INS

$B = I \times 1.2 \times 200 \text{ s} = 24 \times \text{INS}$

$\frac{24 \times \text{INS}}{20 \times \text{INS}} = 1.2 \times 1.2 \times$

# **Computing CPI**

Different types of instructions can take very different amounts of cycles Memory accesses, integer math, floating point, control flow

$$CPI = \sum_{types} \left( Cycles_{type} * Frequency_{type} \right)$$

| Instruction Type | Type Cycles | Type Frequency | Cycles * Freq |

|------------------|-------------|----------------|---------------|

| ALU              | 1           | 50%            | • 5           |

| Load             | 5           | 20%            | (0)           |

| Store            | 3           | 10%            | Ø.3           |

| Branch           | 2           | 20%            | 0,4           |

|                  |             | CPI:           | 2.2           |

## **CPI & Processor Tradeoffs**

| Instruction Type | Type Cycles | Type Frequency |

|------------------|-------------|----------------|

| ALU              | 1           | 50%            |

| Load             | 5           | 20%            |

| Store            | 3           | 10%            |

| Branch           | 2           | 20%            |

- x = 1,22×

How much faster would the machine be if:

- 1. A data cache reduced the average load time to 2 cycles? DLP = 2.2 =  $1.375 \times$ NEW = 1.6

- 2. Branch prediction shaved a cycle off the branch time?

- 3. Two ALU instructions could be executed at once?

$- = | \cdot | \times$

. 2.2

The impact of a performance improvement is limited by what is NOT improved:

Example: Assume a program runs in 100 seconds on a machine, with multiply responsible for 80 seconds of this time. How much do we have to speed up multiply to make the program run 4 times faster?

$OLP = 1005 - 755. = 7205 + \frac{80}{N}$ N = 16.

5 times faster?

#### Warning 2: MIPs, MHz ≠ Performance

Higher MHz (clock rate) doesn't always mean better CPU Orange computer: 1000 MHz, CPI: 2.5, 1 billion instruction program

Grape computer: 500MHz, CPI: 1.1, 1 billion instruction program

Higher MIPs (million instructions per second) doesn't always mean better CPU

1 MHz machine, with two different compilers

Compiler A on program X: 10M ALU, 1M Load

Compiler B on program X: 5M ALU, 1M Load

| Execution Time: A B | Instruction Type | Type Cycles |

|---------------------|------------------|-------------|

|                     | ALU              | 1           |

|                     | Load             | 5           |

|                     | Store            | 3           |

| MIPS: A B           | Branch           | 2           |

Machine performance:

Better performance:

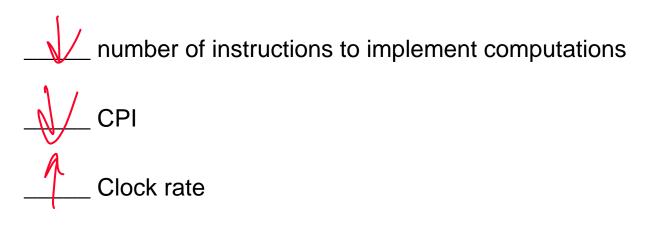

Improving performance must balance each constraint

Example: RISC vs. CISC