# 01 Introduction to Digital Logic

ENGR 3410 - Computer Architecture Mark L. Chang Fall 2009

#### Acknowledgements

- Patterson & Hennessy: Book & Lecture Notes

- Patterson's 1997 course notes (U.C. Berkeley CS 152, 1997)

- Tom Fountain 2000 course notes (Stanford EE182)

- Michael Wahl 2000 lecture notes (U. of Siegen CS 3339)

- Ben Dugan 2001 lecture notes (UW-CSE 378)

- Professor Scott Hauck lecture notes (UW EE 471)

- Mark L. Chang lecture notes for Digital Logic (NWU B01)

### Example: Car Electronics

• Door ajar light (driver door, passenger door):

• High-beam indicator (lights, high beam selected):

## Example: Car Electronics (cont.)

• Seat Belt Light (driver belt in):

• Seat Belt Light (driver belt in, passenger belt in, passenger present):

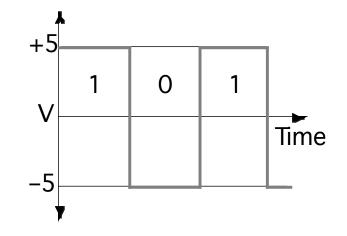

# Digital vs. Analog

+5 V Time

Digital: only assumes discrete values Analog: values vary over a broad range continuously

# Advantages of Digital Circuits

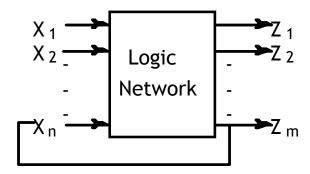

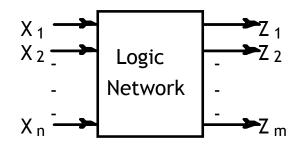

#### Combinational vs. Sequential Logic

#### Sequential logic

Network implemented from logic gates. The presence of feedback distinguishes between *sequential* and *combinational* networks.

#### Combinational logic

No feedback among inputs and outputs. Outputs are a function of the inputs only.

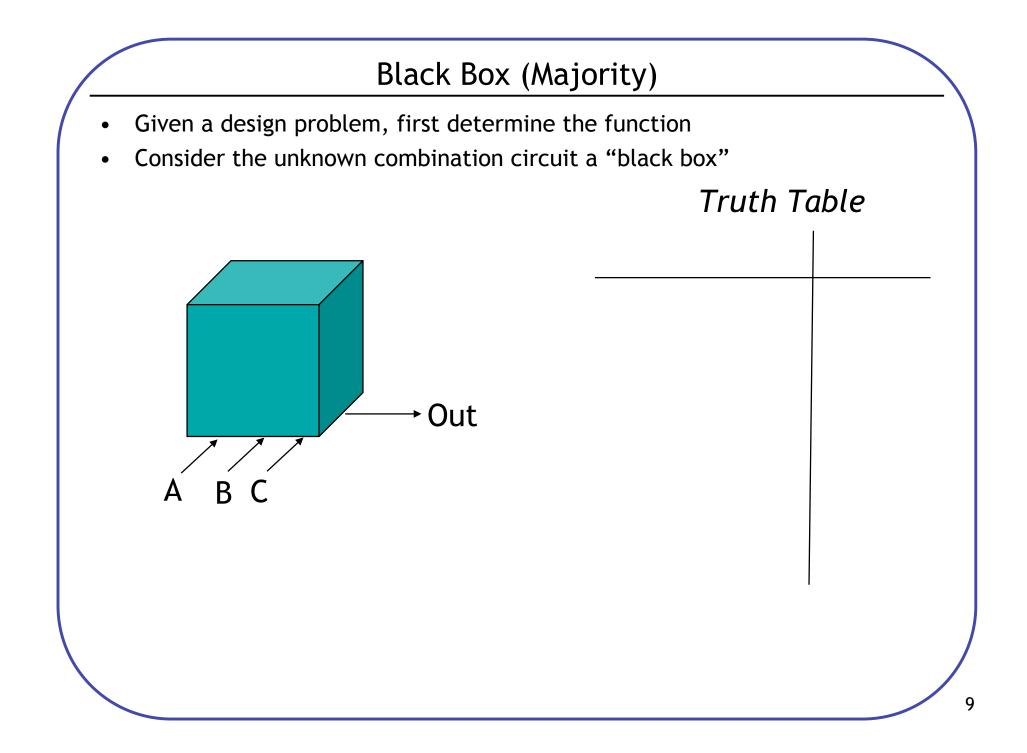

## "Black Box" Design & Truth Tables

- Given an idea of a desired circuit, implement it

- Example: Odd parity inputs: A, B, C, output: Out

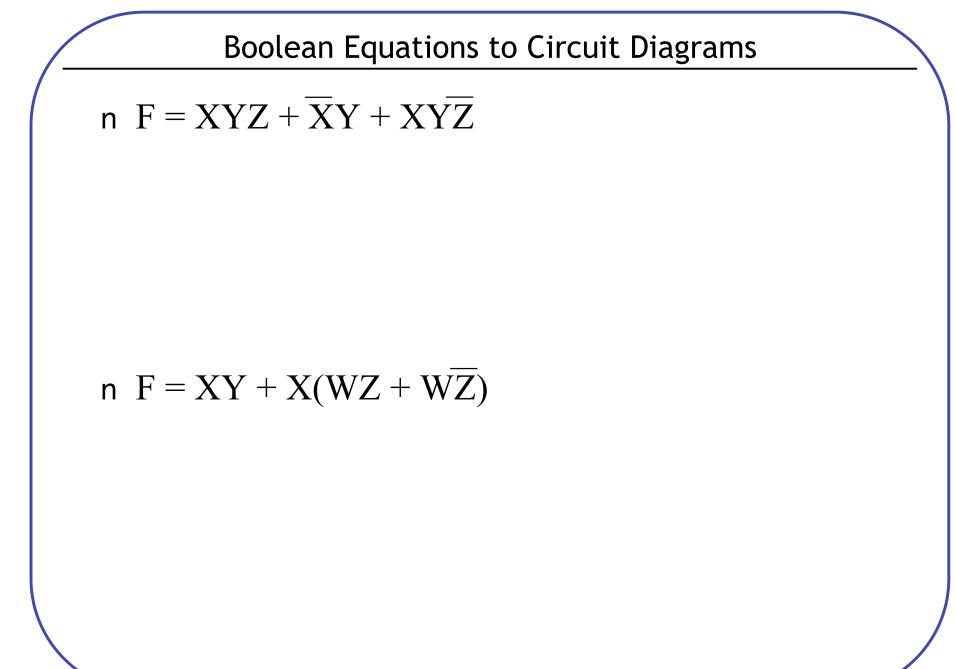

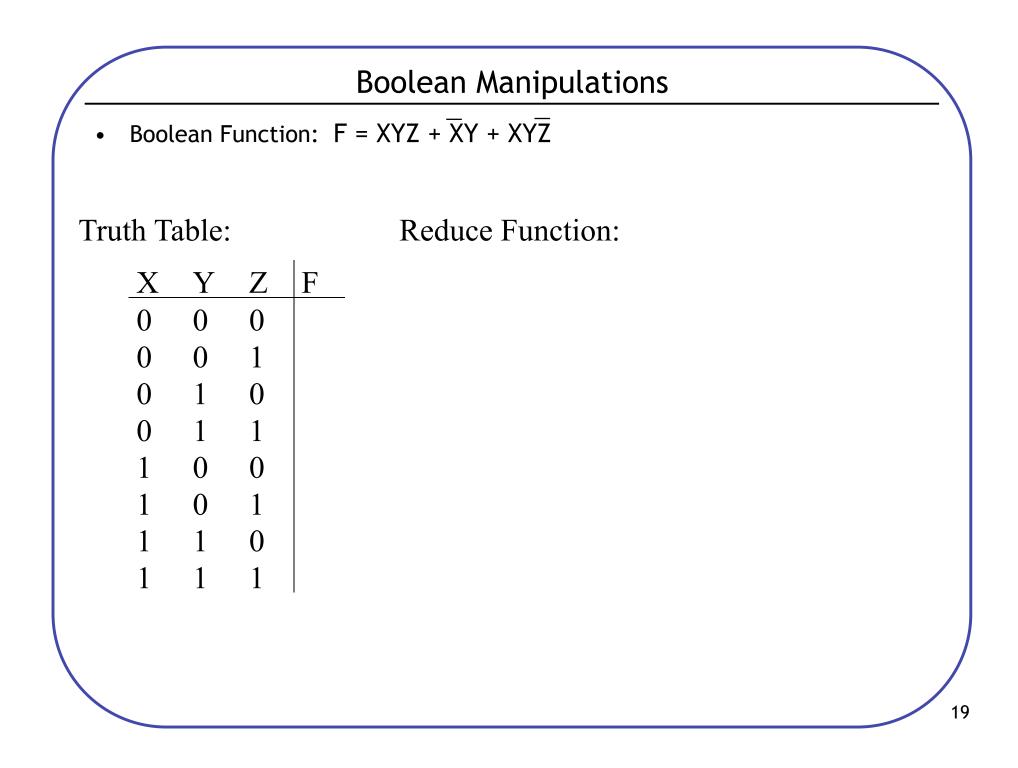

#### **Boolean Equations**

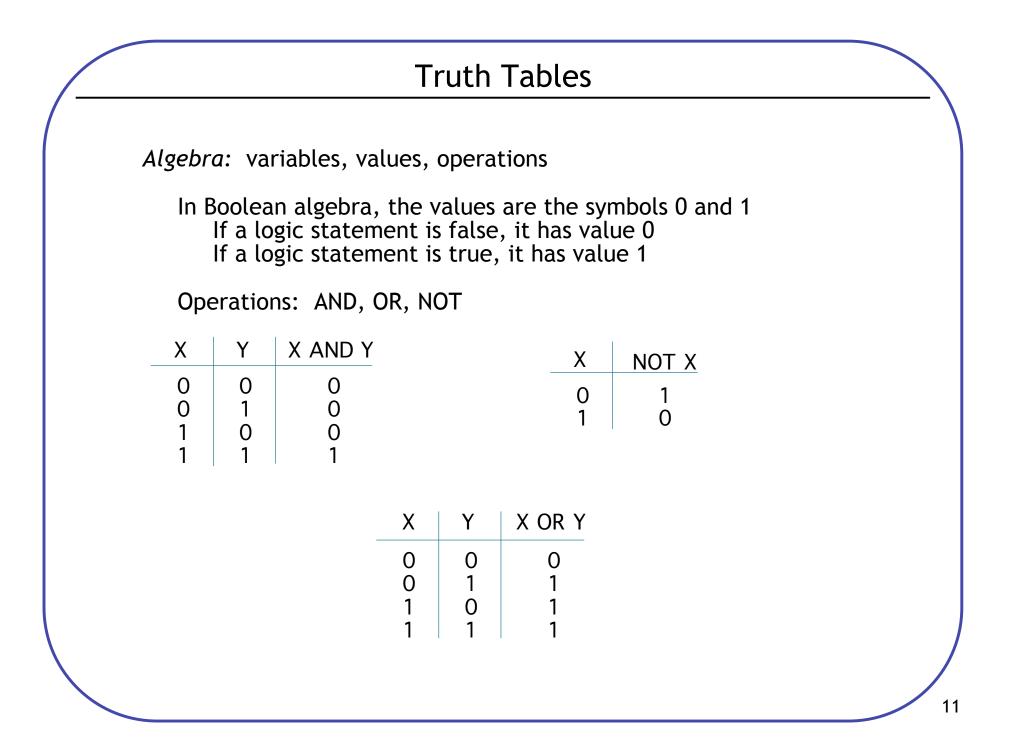

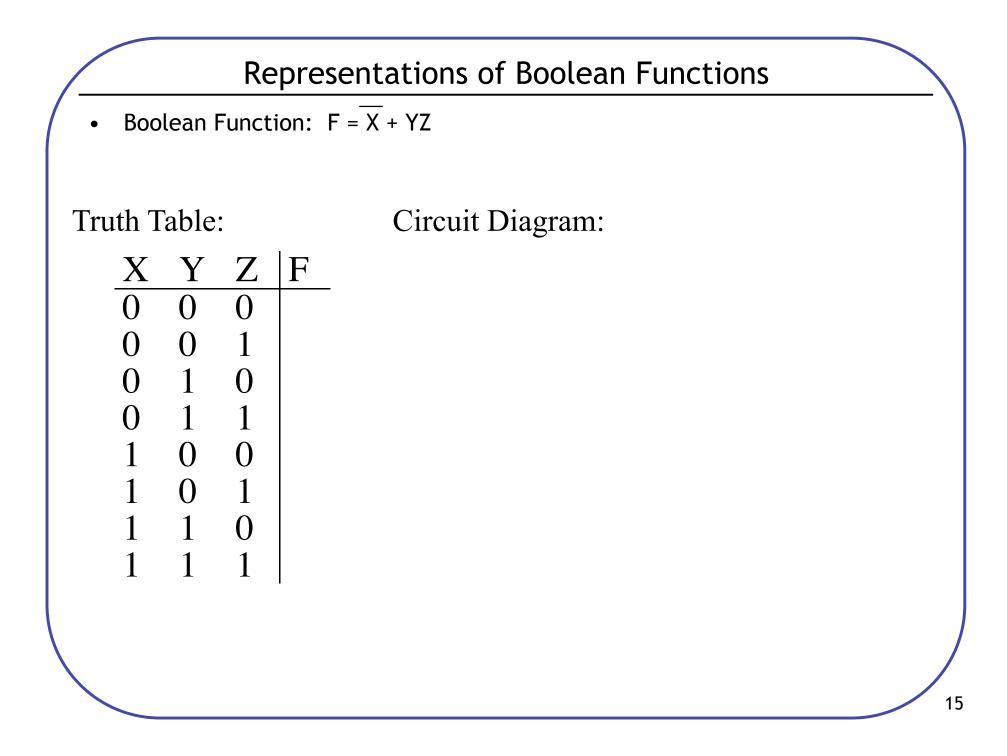

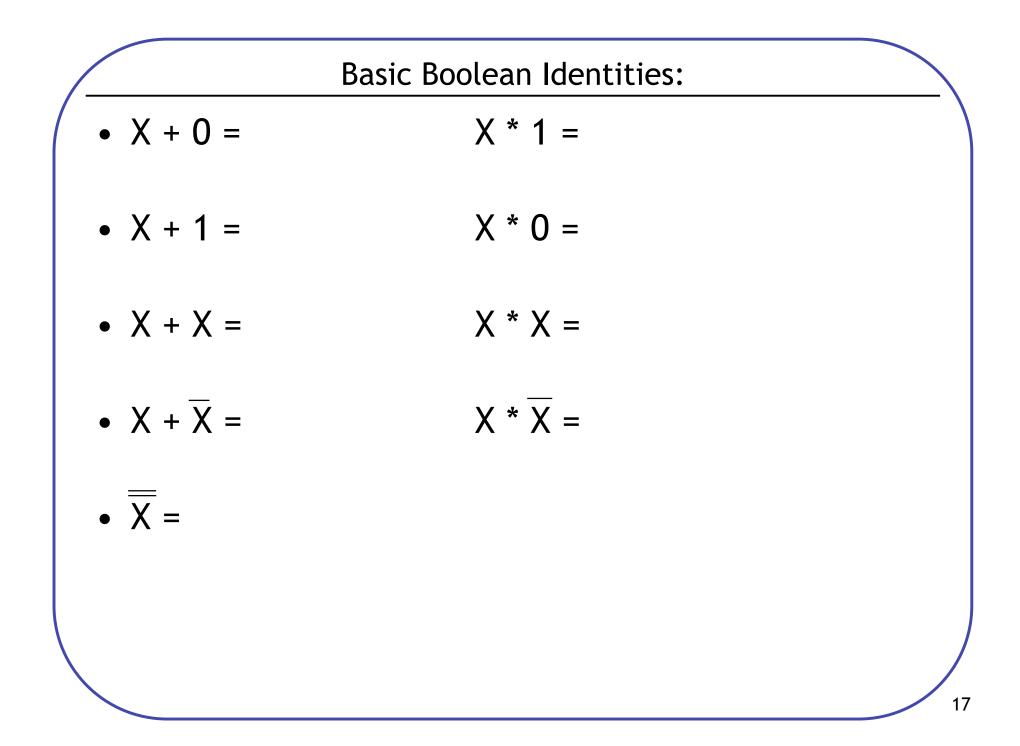

Boolean Algebra values: 0, 1 variables: A, B, C, . . ., X, Y, Z operations: NOT, AND, OR, . . .

NOT X is written as  $\overline{X}$ X AND Y is written as X & Y, or sometimes X Y X OR Y is written as X + Y

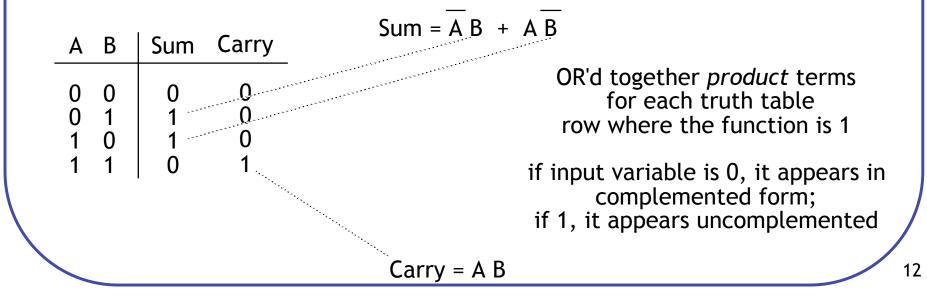

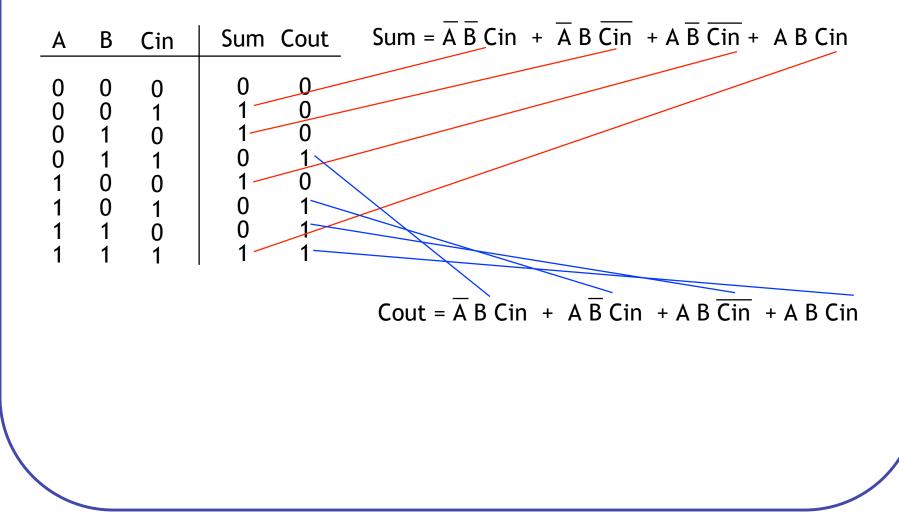

Deriving Boolean equations from truth tables:

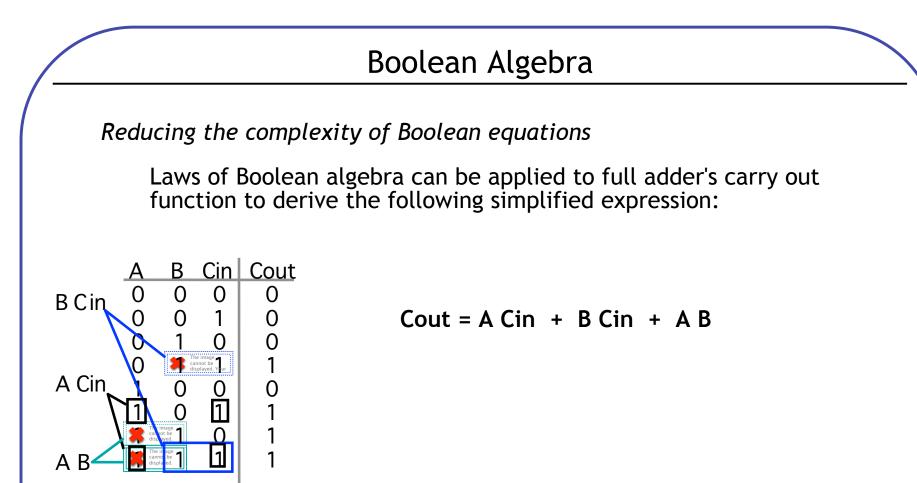

#### Boolean Algebra

Another example:

Verify equivalence with the original Carry Out truth table:

place a 1 in each truth table row where the product term is true

each product term in the above equation covers exactly two rows in the truth table; several rows are "covered" by more than one term

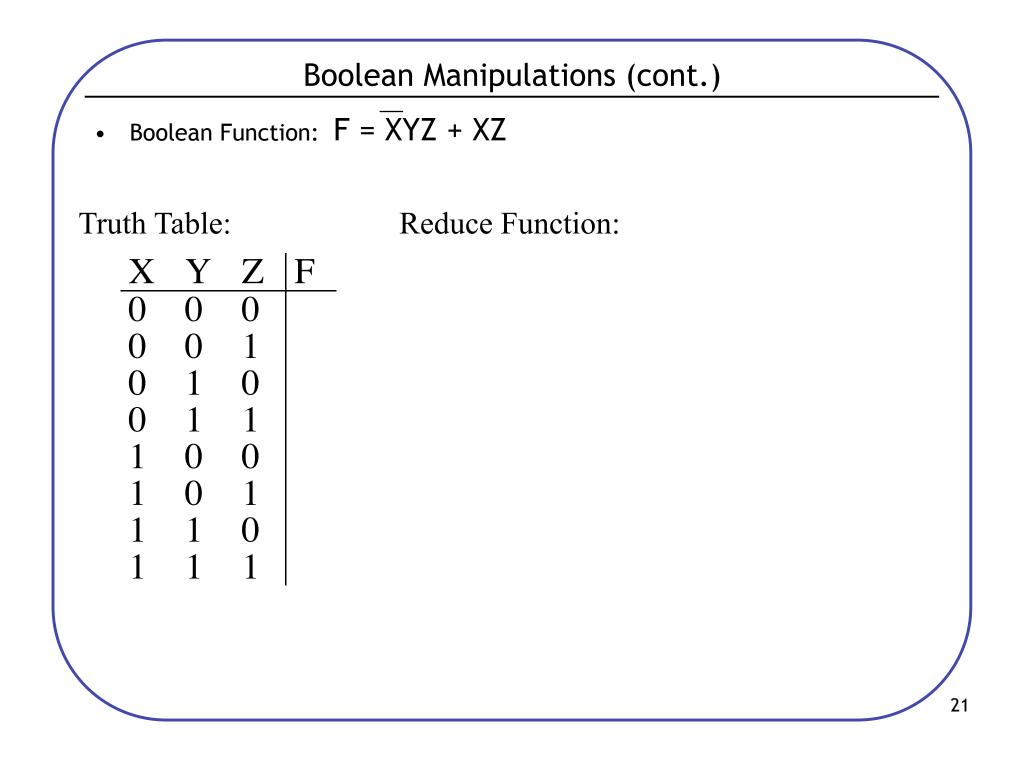

#### Why Boolean Algebra/Logic Minimization?

Logic Minimization: reduce complexity of the gate level implementation

- reduce number of literals (gate inputs)

- reduce number of gates

- reduce number of levels of gates

fewer inputs implies faster gates in some technologies fan-ins (number of gate inputs) are limited in some technologies fewer levels of gates implies reduced signal propagation delays number of gates (or gate packages) influences manufacturing costs

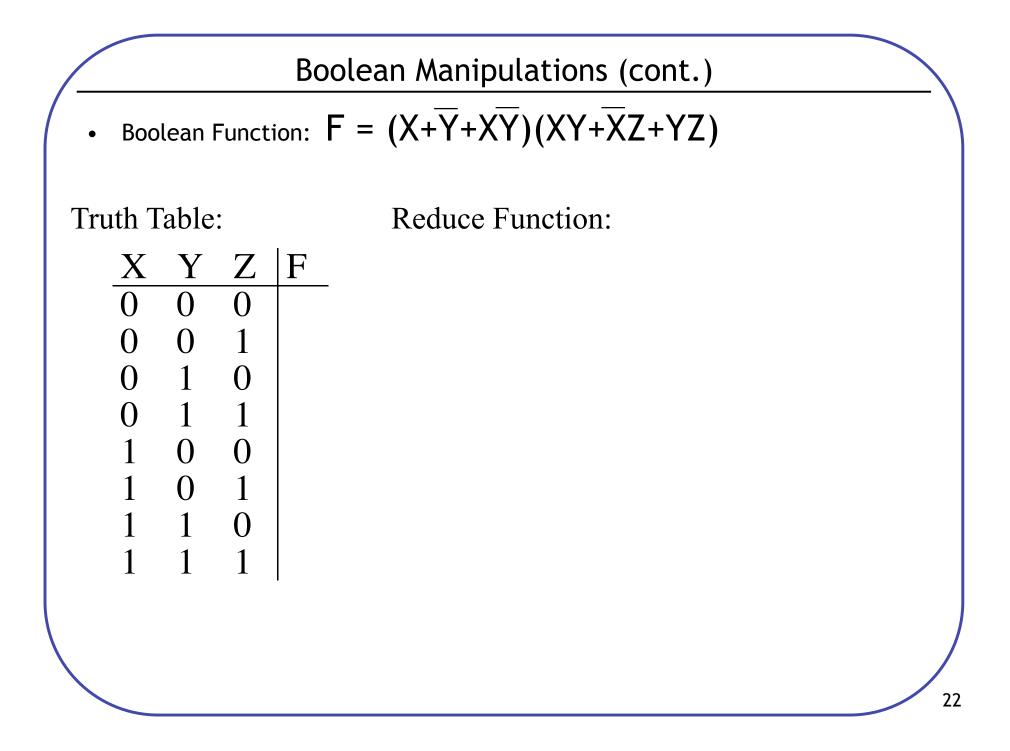

|                                                                 | Basic Laws        |  |

|-----------------------------------------------------------------|-------------------|--|

| <ul> <li>Commutative Law:</li> <li>X + Y = Y + X</li> </ul>     | XY = YX           |  |

| <ul> <li>Associative Law:<br/>X+(Y+Z) = (X+Y)+Z</li> </ul>      | X(YZ)=(XY)Z       |  |

| <ul> <li>Distributive Law:</li> <li>X(Y+Z) = XY + XZ</li> </ul> | X+YZ = (X+Y)(X+Z) |  |

| , (, _), , , , <u>,</u>                                         |                   |  |

## Advanced Laws

- n X+XY = n XY +  $\overline{XY}$  =

- n X+XY =

- n X(X+Y) =

- $\mathsf{n} \ (X{+}Y)(X{+}\overline{Y}) =$

- n  $X(\overline{X}+Y) =$

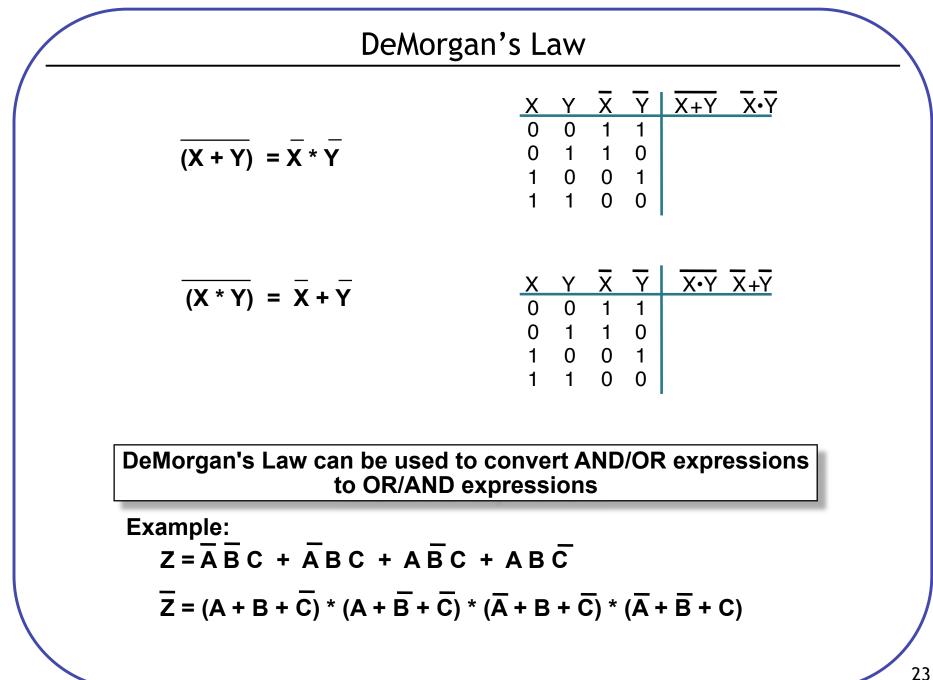

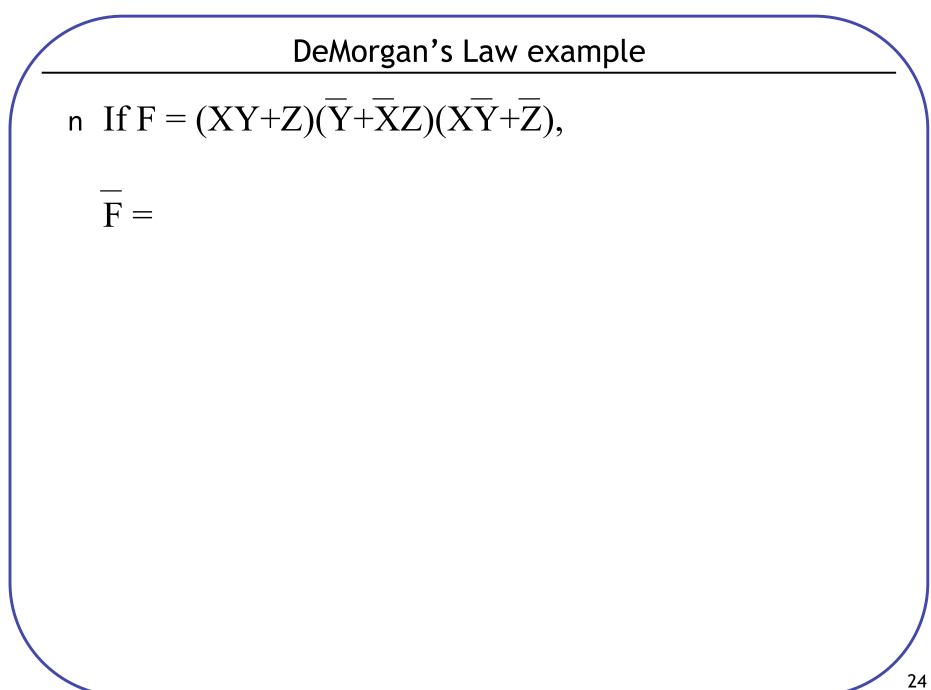

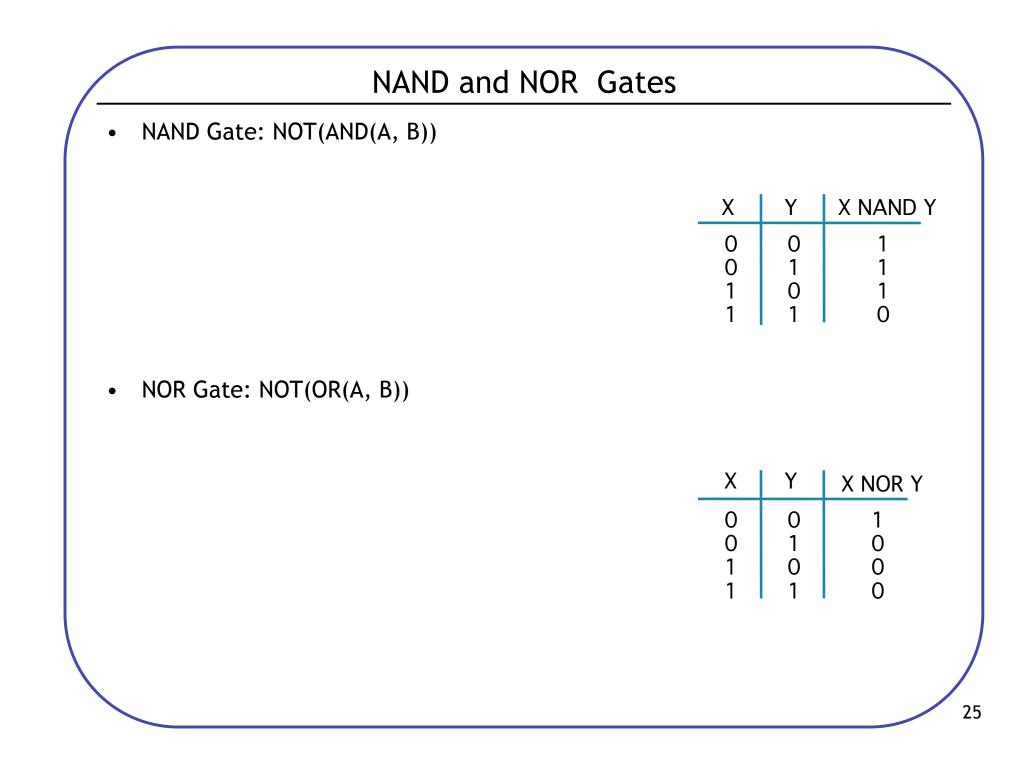

#### NAND and NOR Gates

- NAND and NOR gates are universal

- can implement all the basic gates (AND, OR, NOT)

NOR

#### NOT

AND

OR

# **Bubble Manipulation**

• Bubble Matching

• DeMorgan's Law

27